# MAHENDRA COLLEGE OF ENGINEERING

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

# CS 6211 & IT 6211 - DIGITAL LAB

# LAB MANUAL

Branch: CSE & ITYear/semester: I Year / II Semester

**DIGITAL LAB**

Created by J.SAMPATHKUMAR, AP/ECE

# <u>Syllabus</u>

CS6211

#### DIGITAL LABORATORY

#### **OBJECTIVES:** The student should be made to:

- Understand the various logic gates.

- Be familiar with various combinational circuits.

- Understand the various components used in the design of digital computers.

- Be exposed to sequential circuits

- Learn to use HDL

#### LIST OF EXPERIMENTS:

- 1. Verification of Boolean Theorems using basic gates.

- 2. Design and implementation of combinational circuits using basic gates for arbitrary functions, code converters.

- 3. Design and implementation of combinational circuits using MSI devices:

- 4 bit binary adder / subtractor

- Parity generator / checker

- Magnitude Comparator

- Application using multiplexers

#### 4. Design and implementation of sequential circuits:

- Shift -registers

- Synchronous and asynchronous counters

- 5. Coding combinational / sequential circuits using HDL.

- 6. Design and implementation of a simple digital system (Mini Project).

#### **TOTAL: 45 PERIODS**

#### OUTCOMES: At the end of this course, the student will be able to:

- Use boolean simplification techniques to design a combinational hardware circuit.

- Design and Implement combinational and sequential circuits.

- Analyze a given digital circuit combinational and sequential.

- Design the different functional units in a digital computer system.

- Design and Implement a simple digital system.

#### LABORATORY REQUIREMENT FOR BATCH OF 30 STUDENTS

#### HARDWARE:

- 1. Digital trainer kits 30

- 2. Digital ICs required for the experiments in sufficient numbers 96

#### SOFTWARE:

1. HDL simulator.

|     |                                                                                                 | ECTRONICS LAB |                                                   |  |  |

|-----|-------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------|--|--|

|     | DO'S                                                                                            | DON' TS       |                                                   |  |  |

| 1.  | Be regular to the lab.                                                                          | 1.            | Do not exceed the voltage Rating.                 |  |  |

| 2.  | Follow proper Dress Code.                                                                       | 2.            | Do not inter change the IC's                      |  |  |

| 3.  | Maintain Silence.                                                                               |               | while doing the experiment.                       |  |  |

|     | Know the theory behind the experiment before coming to the lab.                                 |               | short circuits.                                   |  |  |

| 5.  | Identify the different leads or                                                                 | 4.            | Do not throw the connecting wires to floor.       |  |  |

|     | terminals or pins of the IC before making connection.                                           | 5.            | Do not come late to the lab.                      |  |  |

|     | Know the Biasing Voltage required<br>for different families of IC's and                         | 6.            | Do not operate µ p/IC trainer kits unnecessarily. |  |  |

|     | connect the power supply voltage<br>and ground terminals to the<br>respective pins of the IC's. | 7.            | Do not panic if you don't get the output.         |  |  |

|     | Know the Current and Voltage rating of the IC's before using them in the experiment.            |               |                                                   |  |  |

|     | Avoid unnecessary talking while doing the experiment.                                           |               |                                                   |  |  |

| 9.  | Handle the IC Trainer Kit properly.                                                             |               |                                                   |  |  |

|     | Mount the IC Properly on the IC Zif Socket.                                                     |               |                                                   |  |  |

|     | Handle the microprocessor kit properly.                                                         |               |                                                   |  |  |

|     | While doing the Interfacing,<br>connect proper voltages to the<br>interfacing kit.              |               |                                                   |  |  |

| 13. | Keep the Table clean.                                                                           |               |                                                   |  |  |

|     | Take a signature of the In<br>charge before taking the<br>kit/components.                       |               |                                                   |  |  |

|     | After the completion of the experiments switch off the power supply and return the apparatus.   |               |                                                   |  |  |

# The Laboratory Notebook:

Each student must have their own laboratory notebook. All pre-lab exercises and laboratory reports are to be entered into your notebook.

Your notebook must be clearly labeled on the cover with the following information:

| Module             | : | Digital Lab |

|--------------------|---|-------------|

| Name               | : |             |

| <b>Register No</b> | : |             |

| Lab Partner Name   | : |             |

# **Introduction**

There are 3 hours allocated to a laboratory session in Digital Electronics. It is a necessary part of the course at which attendance is compulsory.

Here are some guidelines to help you perform the experiments and to submit the reports:

- 1. Read all instructions carefully and carry them all out.

- 2. Ask a demonstrator if you are unsure of anything.

- 3. Record actual results (comment on them if they are unexpected!)

- 4. Write up full and suitable conclusions for each experiment.

- 5. If you have any doubt about the safety of any procedure, contact the demonstrator beforehand.

- 6. THINK about what you are doing!

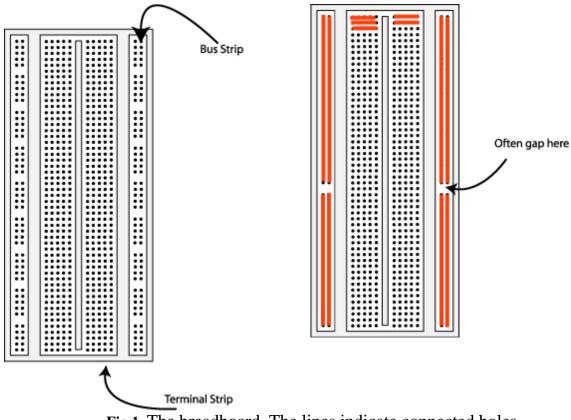

# The Breadboard

The breadboard consists of two terminal strips and two bus strips (often broken in the centre). Each bus strip has two rows of contacts. Each of the two rows of contacts are a node. That is, each contact along a row on a bus strip is connected together (inside the breadboard). Bus strips are used primarily for power supply connections, but are also used for any node requiring a large number of connections. Each terminal strip has 60 rows and 5 columns of contacts on each side of the centre gap. Each row of 5 contacts is a node.

You will build your circuits on the terminal strips by inserting the leads of circuit components into the contact receptacles and making connections with 22-26 gauge wire. There are wire cutter/strippers and a spool of wire in the lab. It is a good practice to wire +5V and 0V power supply connections to separate bus strips.

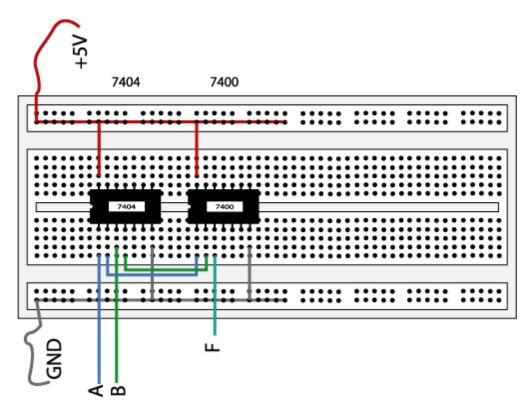

Fig 1. The breadboard. The lines indicate connected holes.

The 5V supply **MUST NOT BE EXCEEDED** since this will damage the ICs (Integrated circuits) used during the experiments. Incorrect connection of power to the ICs could result in them exploding or becoming very hot - with the **possible serious** injury occurring to the people working on the experiment! Ensure that the power supply polarity and all components and connections are correct before switching on power.

# **Building the Circuit:**

Throughout these experiments we will use TTL chips to build circuits. The steps for wiring a circuit should be completed in the order described below:

1. Turn the power (Trainer Kit) off before you build anything!

2. Make sure the power is off before you build anything!

3. Connect the +5V and ground (GND) leads of the power supply to the power and ground bus strips on your breadboard.

4. Plug the chips you will be using into the breadboard. Point all the chips in the same direction with pin 1 at the upper-left corner. (Pin 1 is often identified by a dot or a notch next to it on the chip package)

5. Connect +5V and GND pins of each chip to the power and ground bus strips on the breadboard.

6. Select a connection on your schematic and place a piece of hook-up wire between corresponding pins of the chips on your breadboard. It is better to make the short connections before the longer ones. Mark each connection on your schematic as you go, so as not to try to make the same connection again at a later stage.

7. Get one of your group members to check the connections, **before you turn the power on**.

8. If an error is made and is not spotted before you turn the power on. Turn the power off immediately before you begin to rewire the circuit.

9. At the end of the laboratory session, collect you hook-up wires, chips and all equipment and return them to the demonstrator.

10. Tidy the area that you were working in and leave it in the same condition as it was before you started.

### **Common Causes of Problems**

- 1. Not connecting the ground and/or power pins for all chips.

- 2. Not turning on the power supply before checking the operation of the circuit.

- 3. Leaving out wires.

- 4. Plugging wires into the wrong holes.

- 5. Driving a single gate input with the outputs of two or more gates

- 6. Modifying the circuit with the power on.

In all experiments, you will be expected to obtain all instruments, leads, components at the start of the experiment and return them to their proper place after you have finished the experiment. Please inform the demonstrator or technician if you locate faulty equipment. If you damage a chip, inform a demonstrator, don't put it back in the box of chips for somebody else to use.

# **Example Implementation of a Logic Circuit**

Build a circuit to implement the Boolean function F = /(/A./B), please note that the notation /A refers to  $\overline{A}$ . You should use that notation during the write-up of your laboratory experiments.

Fig 2. The complete designed and connected circuit

Sometimes the chip manufacturer may denote the first pin by a small indented circle above the first pin of the chip. Place your chips in the same direction, to save confusion at a later stage. Remember that you must connect power to the chips to get them to work.

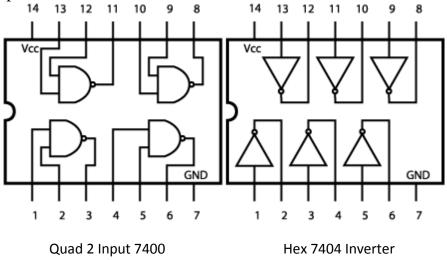

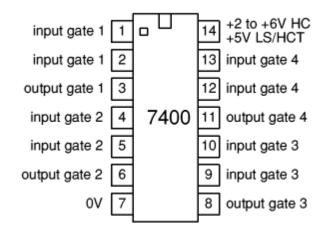

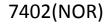

# **Useful IC Pin details**

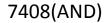

# 7400(NAND)

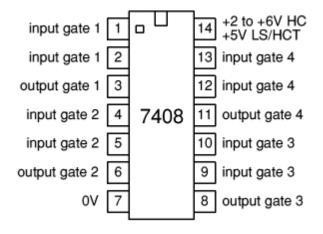

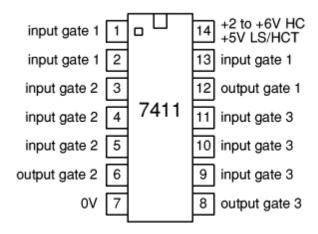

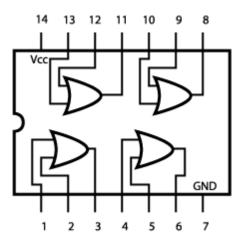

# 7411(3-i/p AND)

7432(OR)

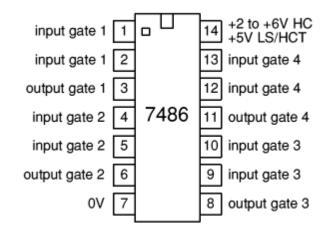

# 7486(EX-OR)

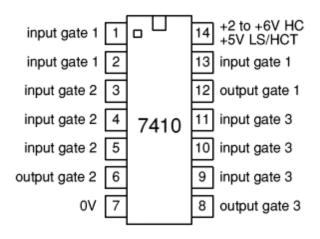

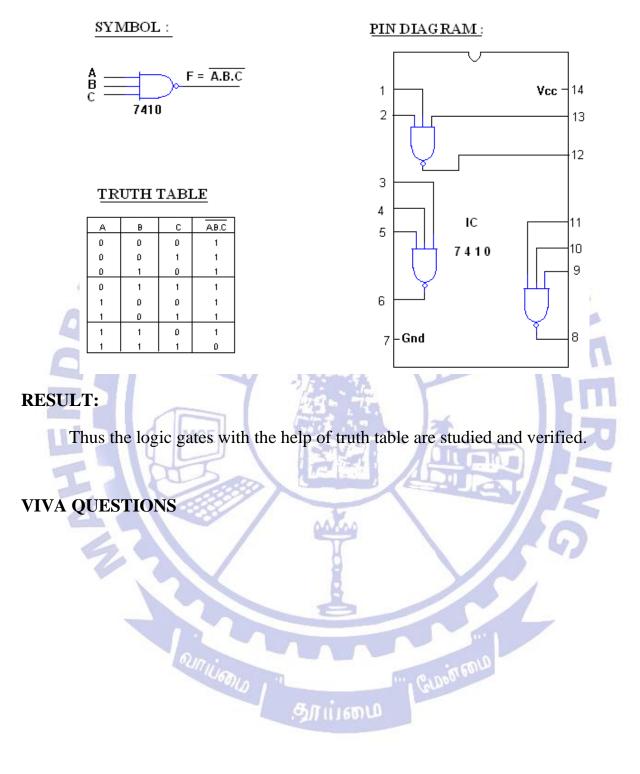

7410(3-i/p NAND)

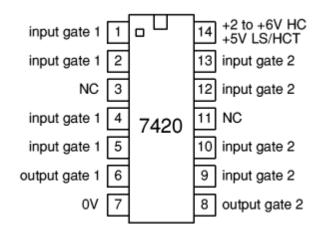

# 7420(4-i/p NAND)

### CS6211 - DIGITAL LAB

#### LIST OF EXPERIMENTS

| S.No | Name of the experiment                                                     |    |  |  |

|------|----------------------------------------------------------------------------|----|--|--|

| 1.   | Study of Logic Gates                                                       | 2  |  |  |

| 2.   | Verification of Boolean Theorems using Logic Gates                         | 7  |  |  |

| 3.   | Design and implementation of adders or substractor using logic gates       | 16 |  |  |

| 4.   | Design & implementation of code convertor                                  | 24 |  |  |

| 5.   | Design of 4-bit adder and subtractor                                       | 35 |  |  |

| 6.   | Parity checker /generator                                                  | 39 |  |  |

| 7.   | Design and implementation of magnitude comparator                          | 47 |  |  |

| 8.   | Design and implementation of multiplexer and demultiplexer                 | 53 |  |  |

| 9.   | Design and implementation of shift register                                | 58 |  |  |

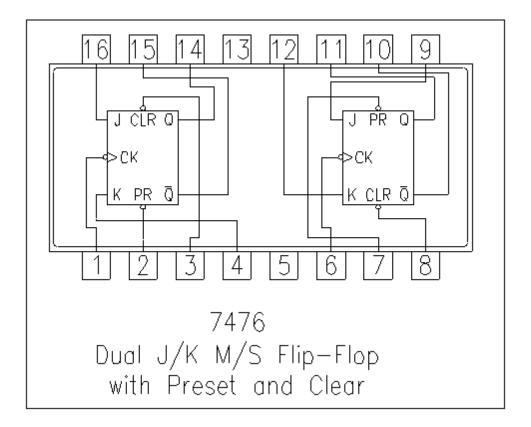

| 10.  | Design and implementation of synchronous / Ripple counter<br>using IC 7476 | 62 |  |  |

| 11.  | Design and implementation synchronous up and Down counter using IC 7476    | 66 |  |  |

| 12.  | Simulation of combinational circuits using HDL                             | 70 |  |  |

| 13.  | Simulation of sequential circuits using HDL                                | 76 |  |  |

| 14.  | Implementation of boolean functions                                        | 81 |  |  |

MAHENDRA COLLEGE OF ENGINEERING

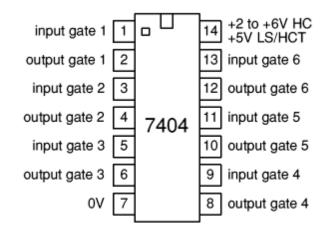

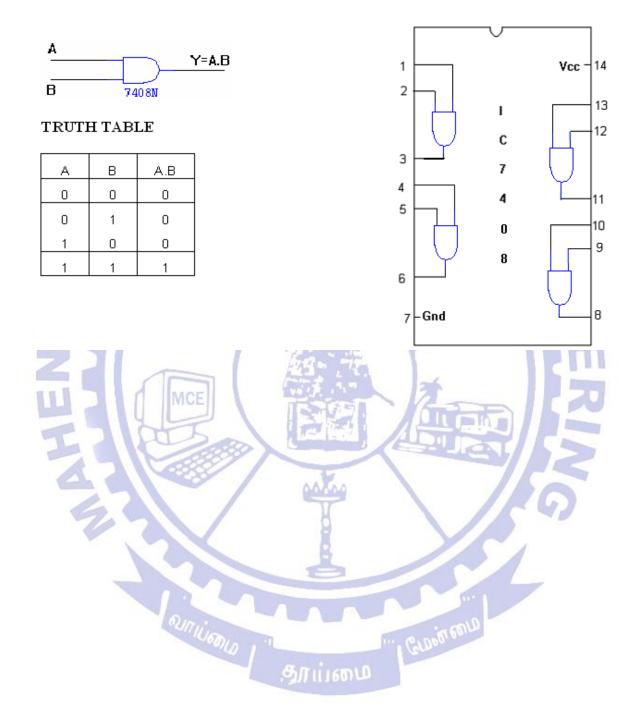

### AND GATE: SYMBOL:

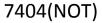

PIN DIAGRAM:

#### MAHENDRA COLLEGE OF ENGINEERING

#### DIGITAL LAB

#### EXP NO: 1

#### STUDY OF LOGIC GATES

#### AIM:

To study about logic gates and verify their truth tables.

#### **APPARATUS REQUIRED:**

| SL No. | COMPONENT       | SPECIFICATION | QTY |

|--------|-----------------|---------------|-----|

| 1.     | AND GATE        | IC 7408       | 1   |

| 2.     | OR GATE         | IC 7432       | 1   |

| 3.     | NOT GATE        | IC 7404       | 1   |

| 4.     | NAND GATE 2 I/P | IC 7400       | 1   |

| 5.     | NOR GATE        | IC 7402       | 1   |

| 6.     | X-OR GATE       | IC 7486       | 1   |

| 7.     | NAND GATE 3 I/P | IC 7410       | 1   |

| 8.     | IC TRAINER KIT  |               | 1   |

| 9.     | PATCH CORD      |               | 14  |

|        |                 |               |     |

#### **THEORY:**

Circuit that takes the logical decision and the process are called logic gates. Each gate has one or more input and only one output. OR, AND and NOT are basic gates. NAND, NOR and X-OR are known as universal gates. Basic gates form these gates.

#### AND GATE:

The AND gate performs a logical multiplication commonly known as AND function. The output is high when both the inputs are high. The output is low level when any one of the inputs is low.

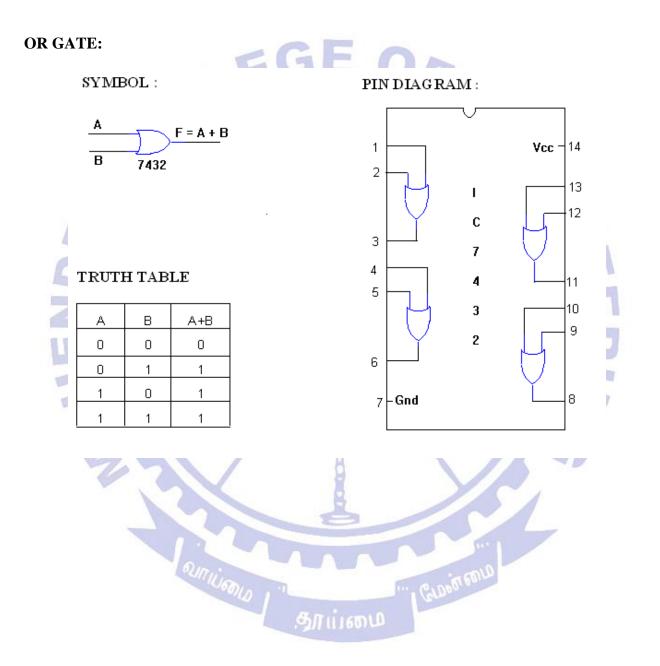

#### **OR GATE:**

The OR gate performs a logical addition commonly known as OR function. The output is high when any one of the inputs is high. The output is low level when both the inputs are low.

#### NOT GATE:

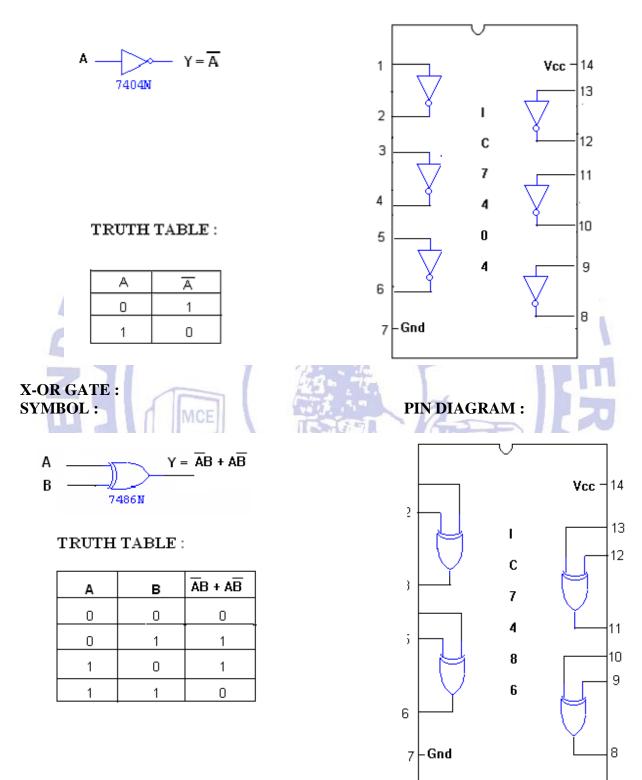

The NOT gate is called an inverter. The output is high when the input is low. The output is low when the input is high.

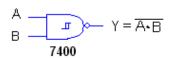

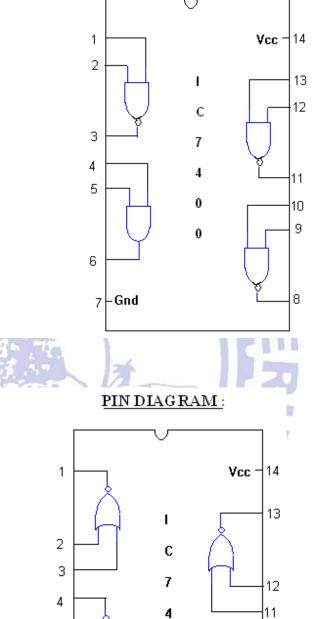

#### NAND GATE:

The NAND gate is a contraction of AND-NOT. The output is high when both inputs are low and any one of the input is low. The output is low level when both inputs are high.

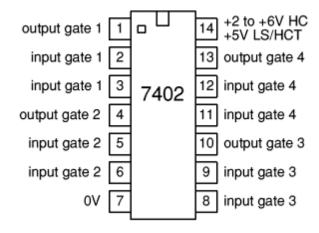

#### NOR GATE:

தாபமை

The NOR gate is a contraction of OR-NOT. The output is high when both inputs are low. The output is low when one or both inputs are high.

#### **X-OR GATE:**

The output is high when any one of the inputs is high. The output is low when both the inputs are low and both the inputs are high.

#### **PROCEDURE:**

- 1. Connections are given as per circuit diagram.

- 2. Logical inputs are given as per circuit diagram.

- 3. Observe the output and verify the truth table.

#### NOT GATE: SYMBOL:

MAHENDRA COLLEGE OF ENGINEERING

# 2-INPUT NAND GATE: SYMBOL:

#### TRUTH TABLE

| А | В | A.B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

0

2

5

6

7-Gnd

SYMBOL :

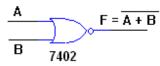

NOR GATE:

1

#### TRUTH TABLE

| А | В | A+B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

J.SAMPATHKUMAR, AP/ECE

10

9

8

#### **3-INPUT NAND GATE :**

#### MAHENDRA COLLEGE OF ENGINEERING

#### DIGITAL LAB

#### EXP NO: 2 VERIFICATION OF BOOLEAN THEOREMS USING LOGIC GATES

#### AIM:

To design the logic circuits and verify its truth table for the following Boolean functions.

#### **APPARATUS REQUIRED:**

| Sl. No. | COMPONENTS  | SPECIFICATION/<br>RANGE | Qty  |

|---------|-------------|-------------------------|------|

| 1.      | AND GATE    | IC 7408                 | 1    |

| 2.      | OR GATE     | IC 7432                 | 1    |

| 3.      | NOT GATE    | IC 7404                 | 1    |

| 4.      | DIGITAL     |                         |      |

| _       | TRAINER KIT |                         | 164  |

| 5.      | CONNECTING  |                         | Req. |

| YC      | WIRES       |                         |      |

#### **THEORY:**

Boolean theorems can help us to simplify logic expressions and logic circuits. Boolean algebra is an individual tool in describing, analyzing, designing and implementing digital circuits.

### **BASIC BOOLEAN LAWS**

#### 1. Commutative Law

The binary operator OR, AND is said to be commutative if,

1. A+B = B+A 2. A.B=B.A

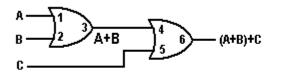

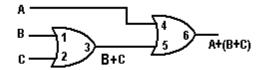

#### 2. Associative Law

The binary operator OR, AND is said to be associative if,

1. A+(B+C) = (A+B)+C 2. A.(B.C) = (A.B).C

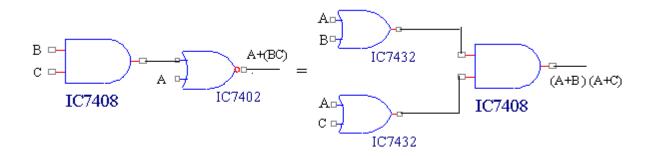

#### 3. Distributive Law

The binary operator OR, AND is said to be distributive if,

1. A+(B.C) = (A+B).(A+C) 2. A.(B+C) = (A.B)+(A.C) Giandino

4. Absorption Law

1. A + AB = A

2.

$$A + \overline{A}B = A + B$$

J.SAMPATHKUMAR, AP/ECE

#### MAHENDRA COLLEGE OF ENGINEERING

#### 5. Involution (or) Double complement Law

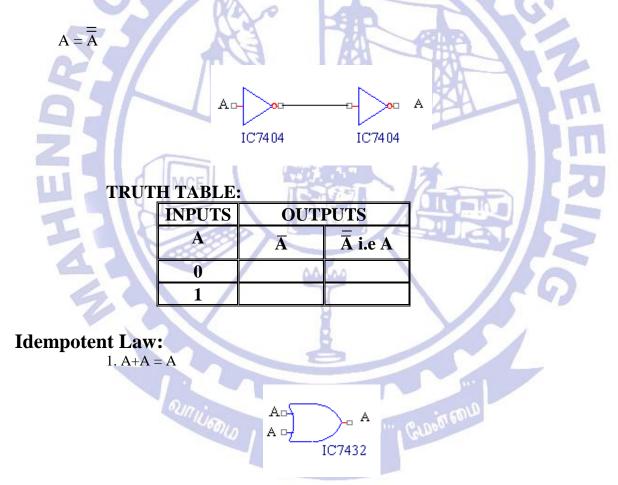

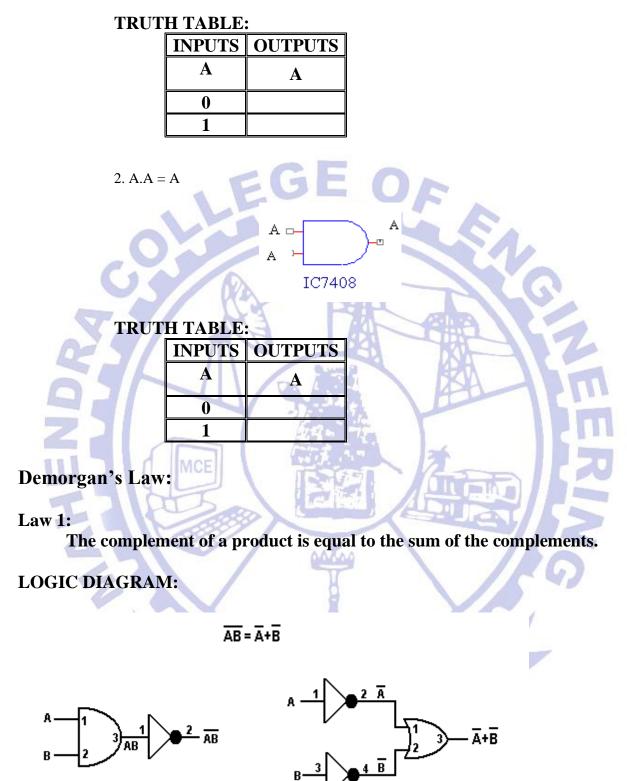

6. Idempotent Law

1.  $\overline{\overline{A}} = A$

1. A+A = A 2. A.A = A

#### 7. Complementary Law

1. A+A' = 1 2. A.A' = 0

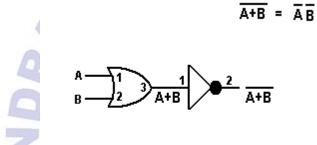

#### 8. De Morgan's Theorem

1. The complement of the sum is equal to the sum of the product of the individual complements.

#### A+B = A.B

2. The complement of the product is equal to the sum of the individual complements.

A.B = A+B

#### 9. Consensus Theorem

Consensus theorem is used to simplify the Boolean expression by eliminating the redundant terms.

AB+A'C+BC = AB+A'CProof: AB+A'C+BC = AB+A'C+BC (A+A') = AB+A'C+ABC+A'BC = AB(1+C)+A'C(1+B) = AB+A'C. (using OR law, 1+C=1 and 1+B=1)

# **Design:**

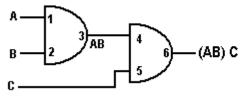

Associative Law: Law 1:

A+(B+C) = (A+B)+CLOGIC DIAGRAM:

MAHENDRA COLLEGE OF ENGINEERING

### **TRUTH TABLE:**

|   | INPUTS |   | OUTPUTS |                                   |     |         |

|---|--------|---|---------|-----------------------------------|-----|---------|

| Α | В      | С | A+B     | ( <b>A</b> + <b>B</b> )+ <b>C</b> | B+C | A+(B+C) |

| 0 | 0      | 0 |         |                                   |     |         |

| 0 | 0      | 1 |         |                                   |     |         |

| 0 | 1      | 0 |         |                                   |     |         |

| 0 | 1      | 1 |         |                                   |     |         |

| 1 | 0      | 0 |         |                                   |     |         |

| 1 | 0      | 1 |         |                                   |     |         |

| 1 | 1      | 0 |         | 5                                 |     |         |

| 1 | 1      | 1 |         | 7                                 |     |         |

-

$$= \begin{array}{c} A \\ B \\ C \\ C \end{array} \begin{array}{c} 1 \\ 2 \end{array} \begin{array}{c} 3 \\ (BC) \end{array} \begin{array}{c} 4 \\ 5 \end{array} \begin{array}{c} 6 \\ A \\ (BC) \end{array}$$

| TRUTH TABLE: | MCE |

|--------------|-----|

|     | INPUTS |       |      | OUT        |     |                |

|-----|--------|-------|------|------------|-----|----------------|

| Α   | B      | С     | A.B  | (A.B).C    | B.C | <b>A.(B.C)</b> |

| 0   | 0      | 0     | V    |            |     |                |

| 0   | 0      | 1     | 2000 |            |     |                |

| 0 🥌 |        | 0     | 8    |            |     |                |

| 0   | 1      | 1     | No.  |            |     |                |

| 1   | 0      | 0     | 2    |            |     |                |

| 1   | 0      |       |      |            |     |                |

| 1   | 1      | 0     |      |            |     |                |

| 1   | 1      | Nig 1 |      | in a min 6 | nu  |                |

|     |        |       |      | 1600       |     |                |

<u>।</u> संसन्ध

தாய்மை

20

MAHENDRA COLLEGE OF ENGINEERING

DIGITAL LAB

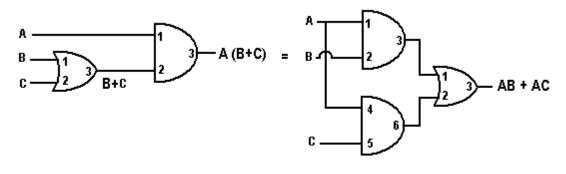

**Distributive Law:**

A (B+C) = AB + AC

**LOGIC DIAGRAM:**

| TRUTH | TABLE: |     | 20   | 1 6     |      |    |       |  |

|-------|--------|-----|------|---------|------|----|-------|--|

|       | INPUTS |     | Y.   | OUTPUTS |      |    |       |  |

| Α     | В      | C   | B+C  | A(B+C)  | AB   | AC | AB+AC |  |

| 0     | 0      | 0   | 2    | 9       | TX1- |    |       |  |

| 0     | 0      |     | (D)  |         | KA   |    | -     |  |

| 0     | 1      | 0   |      | 12.1    |      |    | N H H |  |

| 0     | 1      | 1   |      |         |      |    |       |  |

| 1     | 0      | 0   |      |         | -    |    |       |  |

| 1     | 0      | MCE | KT / | 1 total | 125  | 5  |       |  |

| 1     | 1      | 0   |      |         |      |    |       |  |

| 1     | 1      | 100 | 8/5  |         |      |    |       |  |

Absorption Law:

$$A + AB = A$$

. Geniorenia

#### MAHENDRA COLLEGE OF ENGINEERING

#### DIGITAL LAB

### **TRUTH TABLE:**

| INP | UTS | OUTPUTS |        |  |

|-----|-----|---------|--------|--|

| Α   | В   | A.B     | A+(AB) |  |

|     |     |         | i.e A  |  |

| 0   | 0   |         |        |  |

| 0   | 0   |         |        |  |

| 0   | 1   |         |        |  |

| 0   | 1   | I       |        |  |

| 1   | 0   |         |        |  |

| 1   | 0   |         | 5      |  |

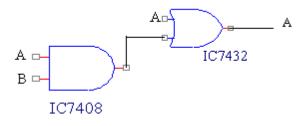

# **Involution (or) Double complement Law:**

В·

#### MAHENDRA COLLEGE OF ENGINEERING

#### DIGITAL LAB

#### **TRUTH TABLE:**

| INP | UTS |    |    | <b>OUTPUTS</b> |   |                                                 |

|-----|-----|----|----|----------------|---|-------------------------------------------------|

| Α   | В   | AB | AB | Ā              | B | $\overline{\mathbf{A}} + \overline{\mathbf{B}}$ |

| 0   | 0   |    |    |                |   |                                                 |

| 0   | 1   |    |    |                |   |                                                 |

| 1   | 0   |    |    |                |   |                                                 |

| 1   | 1   |    | 56 |                |   |                                                 |

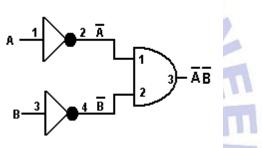

### Law 2:

TRU

The complement of a sum is equal to the product of the Complements. LOGIC DIAGRAM:

| INPU | JTS | 500 |                 | OUTPUTS |   |     |

|------|-----|-----|-----------------|---------|---|-----|

| A    | B   | A+B | <del>A+</del> B | Ā       | Ē | A.B |

| 0    | 0   |     | 0000            |         |   |     |

| 0    | 1   |     | 5               |         |   |     |

| 1    | 0   |     |                 |         |   |     |

| 1    |     |     | h               |         |   |     |

J.SAMPATHKUMAR,AP/ECE

# **Distributive Law:**

A+(B.C) = (A+B).(A+C)

|                     |   |     | 1900       |       |     |             |

|---------------------|---|-----|------------|-------|-----|-------------|

| <b>TRUTH TABLE:</b> |   | 143 | 18         | 180   | all |             |

| INPUTS              |   | T   | BRA        | OUTPU | TS  |             |

| AB                  | С | B.C | A+(B.C)    | A+B   | A+C | (A+B).(A+C) |

| 0 0                 | 0 |     | 1          |       |     |             |

| 0 0                 | 1 |     |            | V     |     |             |

| 0 1                 | 0 | ł   | 14- 75-    |       |     |             |

| 0 1                 | 1 | G   | 12         | 3     |     |             |

| 1 0                 | 0 | 1   |            |       | E   |             |

| 1 0                 | A |     |            |       |     |             |

| 1 1                 | 0 | 897 |            |       | S   |             |

| 1 1                 |   |     |            |       |     |             |

|                     |   |     | Latin Manu |       |     |             |

### **PROCEDURE:**

- 1. Circuit connections are given as per in the given circuit diagram.

- 2. Power supply is switched on.

- 3. The various set of inputs are given and the corresponding outputs are obtained.

- 4. The outputs are verified with the truth table.

# **RESULT:**

Thus the truth tables for the Boolean function are verified.

MAHENDRA COLLEGE OF ENGINEERING

# **VIVA QUESTIONS**

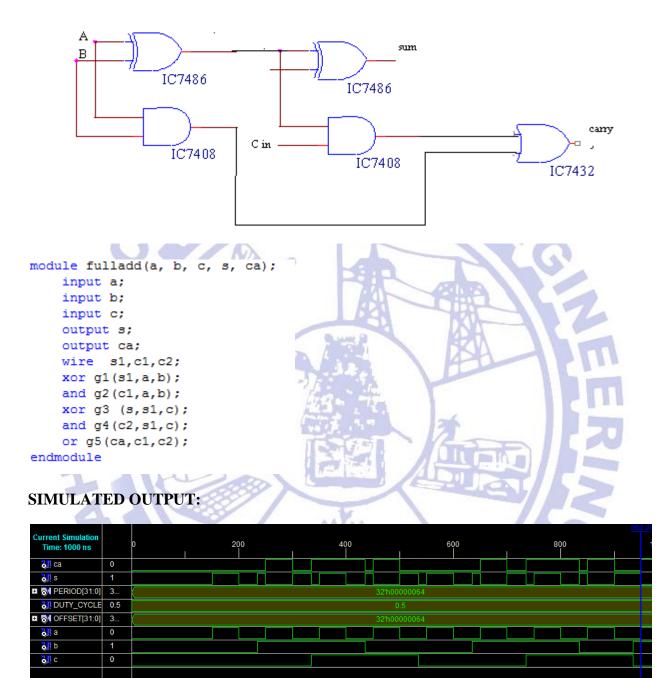

#### EXP.NO: 3

# DESIGN AND IMPLEMENTATION OF ADDERS OR SUBSTRACTOR USING LOGIC GATES

## AIM:

To design and construct half adder, full adder, half subtractor and full subtractor circuits and verify the truth table using logic gates.

# **APPARATUS REQUIRED:**

| Sl.No. | COMPONENT      | SPECIFICATION | QTY. |

|--------|----------------|---------------|------|

| 1.     | AND GATE       | IC 7408       | 1    |

| 2.     | X-OR GATE      | IC 7486       | 1    |

| 3.     | NOT GATE       | IC 7404       | -1   |

| 4.     | OR GATE        | IC 7432       | 1    |

| 3.     | IC TRAINER KIT |               |      |

| 4.     | PATCH CORDS    |               | Req. |

#### **PROCEDURE:**

- 1. Circuit connections are given as per in the diagram.

- 2. Power supply is switched on.

- 3. All the set of inputs are given and the corresponding outputs are verified with truth table.

- 4. Same procedure is followed for all set laws.

MAHENDRA COLLEGE OF ENGINEERING

#### HALF ADDER:

# LOGIC DIAGRAM:

### **TRUTH TABLE:**

| INPU | TS   | OUT | TPUTS |

|------|------|-----|-------|

| A    | В    | SUM | CARRY |

|      | 0    | 0   | 0     |

| 0    | 1    |     | 0     |

|      | 0    |     | 0     |

| 1    | 1 -2 | 0   | 1     |

|      | i ke |     |       |

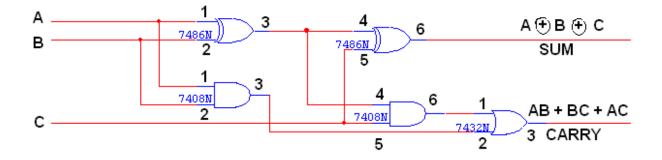

#### **FULL ADDER:**

# LOGIC DIAGRAM:

### FULL ADDER USING TWO HALF ADDER

## **TRUTH TABLE:**

| INPUTS |     |        | OUTPUTS |       |  |

|--------|-----|--------|---------|-------|--|

| A      | В   | С      | SUM     | CARRY |  |

| 0      | 0   | 0      | 0       | 0     |  |

| 0      | 0   | 1-1-   | 1       | 0     |  |

| 0      |     | 0      | 1       | 0     |  |

| 0      | MOE | 1      | 0       | 1     |  |

| 1      |     | 0      |         | 0     |  |

| 1      | 0   |        |         |       |  |

| 1      |     | 0      | 0       |       |  |

|        | 1   | 001000 | 1       |       |  |

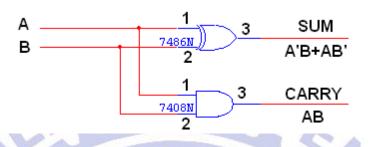

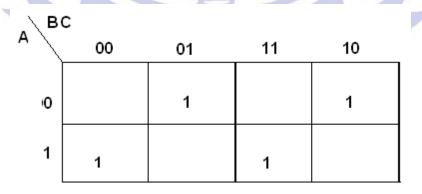

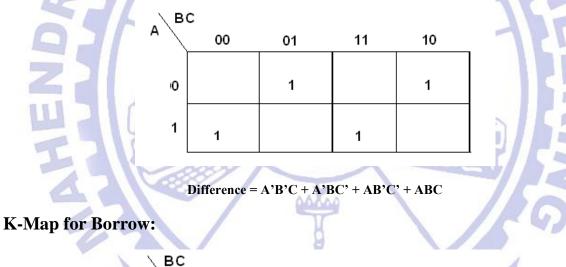

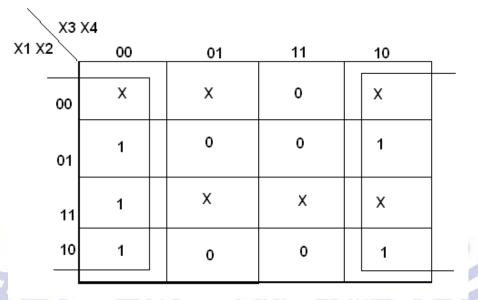

# K-Map for SUM:

SUM = A'B'C + A'BC' + ABC' + ABC

J.SAMPATHKUMAR,AP/ECE

#### **THEORY:**

#### HALF ADDER:

A half adder has two inputs for the two bits to be added and two outputs one from the sum 'S' and other from the carry 'c' into the higher adder position. Above circuit is called as a carry signal from the addition of the less significant bits sum from the X-OR Gate the carry out from the AND gate.

#### **FULL ADDER:**

A full adder is a combinational circuit that forms the arithmetic sum of input; it consists of three inputs and two outputs. A full adder is useful to add three bits at a time but a half adder cannot do so. In full adder sum output will be taken from X-OR Gate, carry output will be taken from OR Gate.

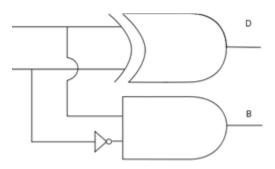

### HALF SUBTRACTOR:

The half subtractor is constructed using X-OR and AND Gate. The half subtractor has two input and two outputs. The outputs are difference and borrow. The difference can be applied using X-OR Gate, borrow output can be implemented using an AND Gate and an inverter.

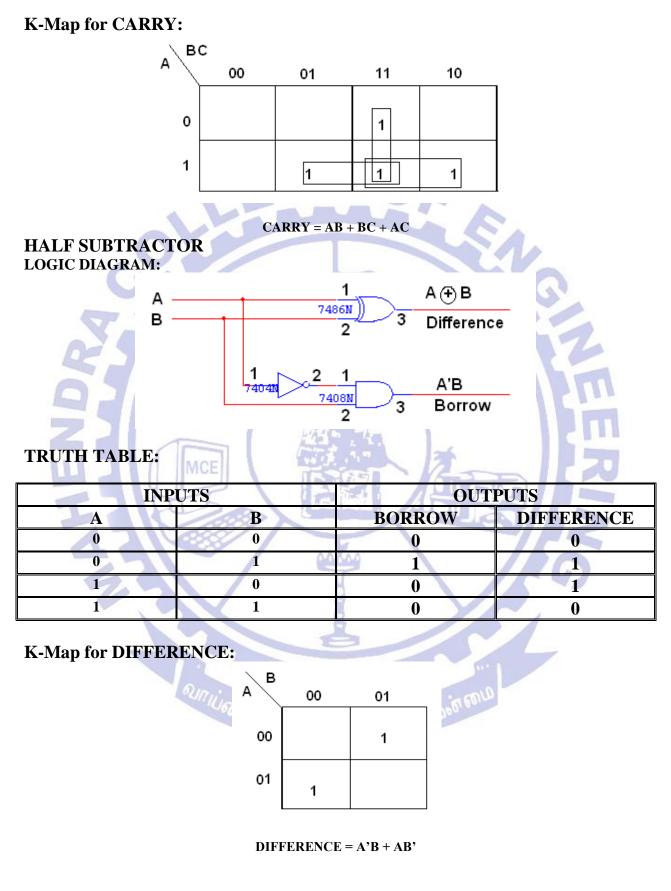

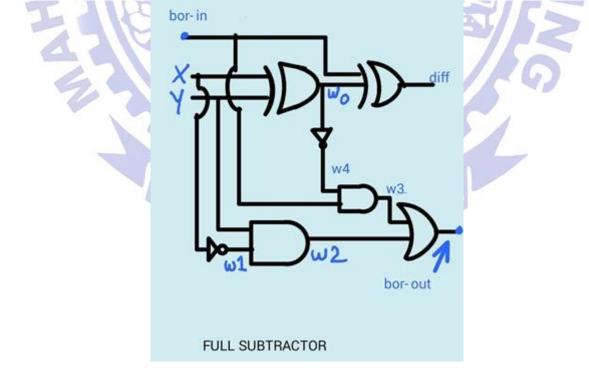

#### **FULL SUBTRACTOR:**

The full subtractor is a combination of X-OR, AND, OR, NOT Gates. In a full subtractor the logic circuit should have three inputs and two outputs. The two half subtractor put together gives a full subtractor .The first half subtractor will be C and A B. The output will be difference output of full subtractor. The expression AB assembles the borrow output of the half subtractor and the second term is the inverted difference output of first X-OR.

லாய்பை தாய்மை

Genistenen

MAHENDRA COLLEGE OF ENGINEERING

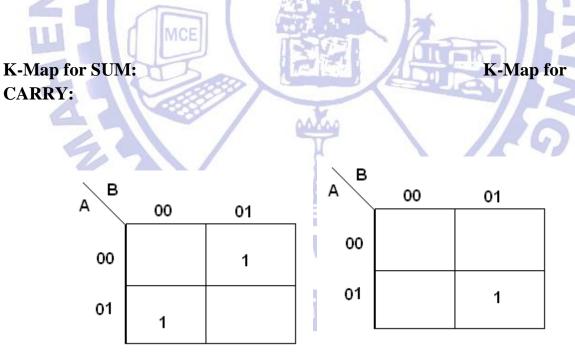

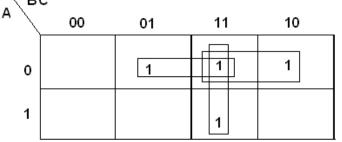

## K-Map for BORROW:

#### DIGITAL LAB

### **TRUTH TABLE:**

|   | INPUTS | OUTPUTS |        |            |

|---|--------|---------|--------|------------|

| Α | В      | С       | BORROW | DIFFERENCE |

| 0 | 0      | 0       | 0      | 0          |

| 0 | 0      | 1       | 1      | 1          |

| 0 | 1      | 0       | 1      | 1          |

| 0 | 1 🗾    | GE      | 1      | 0          |

| 1 | 0      | 0       | 0      | 1          |

| 1 | 0      |         | 0      | 0          |

| 1 | 1      | 0       | 0      | 0          |

| 1 | 1      | 1       | 1      | 1          |

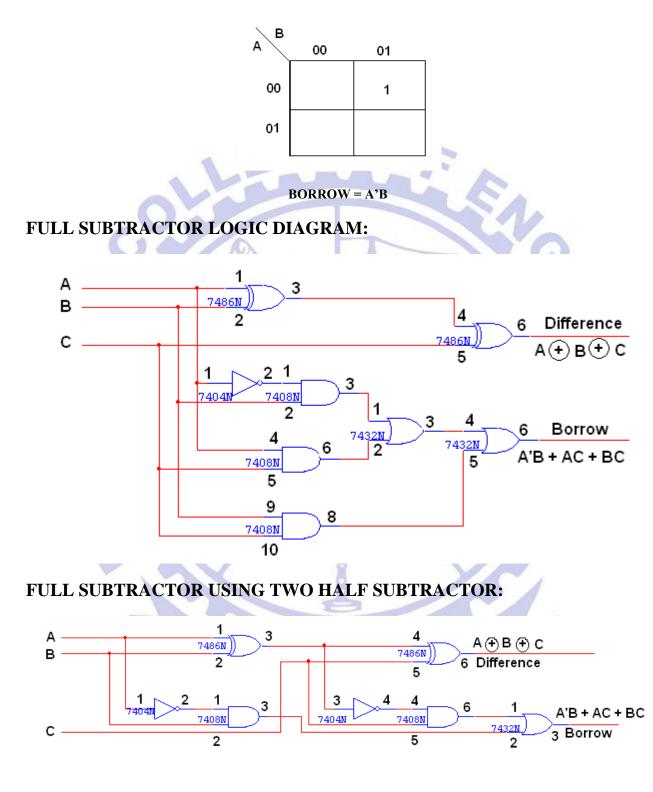

# K-Map for Difference:

Borrow = A'B + BC + A'C

#### EXP NO: 4

### **DESIGN & IMPLEMENTATION OF CODE CONVERTOR**

### AIM:

To design and implement 4-bit

- (i) Binary to gray code converter

- (ii) Gray to binary code converter

- (iii) BCD to excess-3 code converter

- (iv) Excess-3 to BCD code converter

### **APPARATUS REQUIRED:**

| Sl. No. | COMPONENTS          | SPECIFICATION/ RANGE | Qty  |

|---------|---------------------|----------------------|------|

| 1.      | X-OR GATE           | IC 7486              | 2    |

| 2.      | AND GATE            | IC 7408              | 1    |

| 3.      | NOT GATE            | IC 7404              | 1    |

| 4.      | OR GATE             | IC 7432              | 1    |

| 5.      | DIGITAL TRAINER KIT |                      |      |

| 6.      | CONNECTING WIRES    |                      | Req. |

|         |                     |                      |      |

## **THEORY:**

The availability of large variety of codes for the same discrete elements of information results in the use of different codes by different systems. A conversion circuit must be inserted between the two systems if each uses different codes for same information. Thus, code converter is a circuit that makes the two systems compatible even though each uses different binary code.

The bit combination assigned to binary code to gray code. Since each code uses four bits to represent a decimal digit. There are four inputs and four outputs. Gray code is a non-weighted code.

The input variable are designated as B3, B2, B1, B0 and the output variables are designated as C3, C2, C1, Co. from the truth table, combinational circuit is designed. The Boolean functions are obtained from K-Map for each output variable.

A code converter is a circuit that makes the two systems compatible even though each uses a different binary code. To convert from binary code to Excess-3 code, the input lines must supply the bit combination of elements as specified by code and the output lines generate the corresponding bit combination of code. Each one of the four maps represents one of the four outputs of the circuit as a function of the four input variables.

A two-level logic diagram may be obtained directly from the Boolean expressions derived by the maps. These are various other possibilities for a logic

diagram that implements this circuit. Now the OR gate whose output is C+D has been used to implement partially each of three outputs.

# **PROCEDURE:**

- (i) Connections were given as per circuit diagram.

- (ii) Logical inputs were given as per truth table

- (iii) Observe the logical output and verify with the truth tables

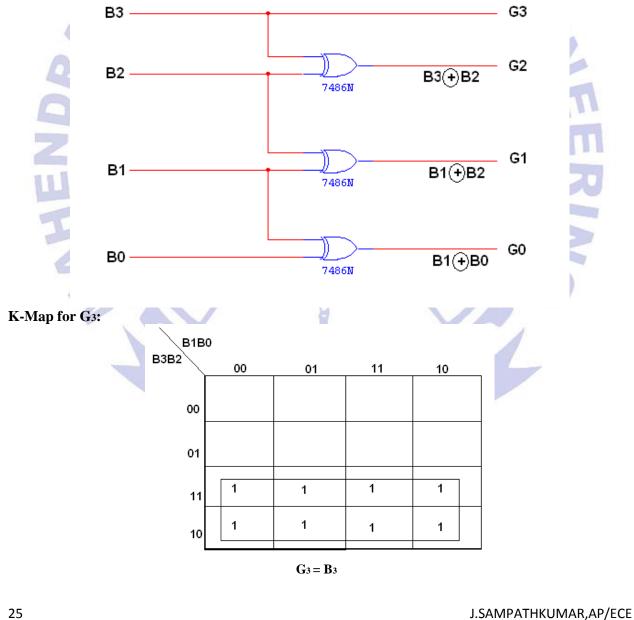

# **LOGIC DIAGRAM: BINARY TO GRAY CODE CONVERTOR**

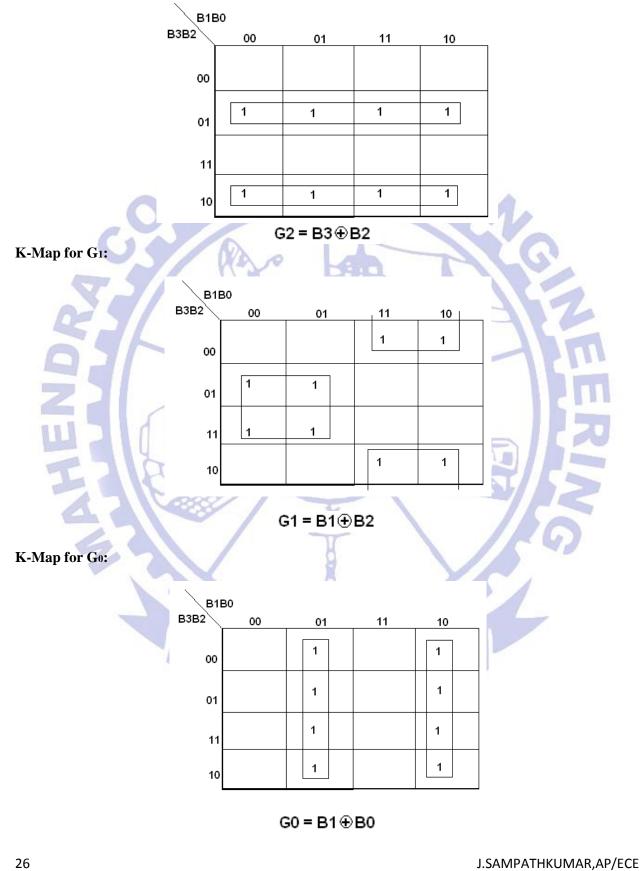

#### K-Map for G2:

26

#### MAHENDRA COLLEGE OF ENGINEERING

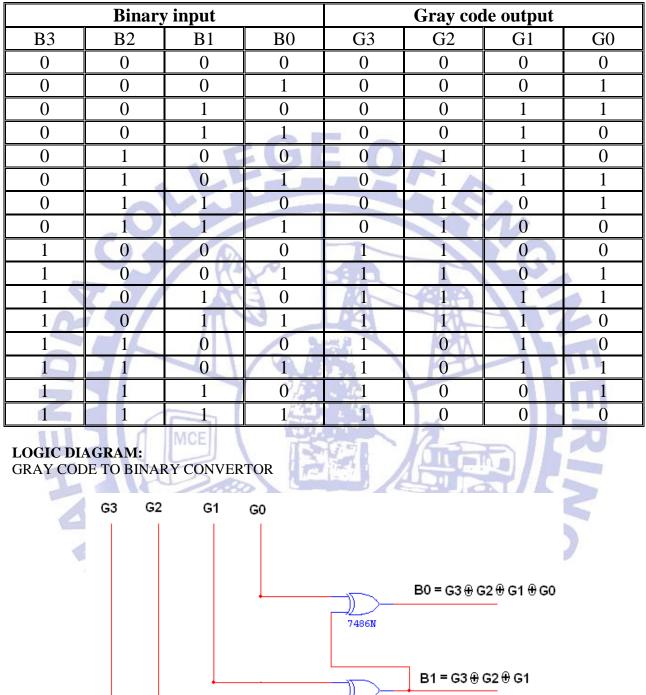

#### **TRUTH TABLE:**

7486N

7486N

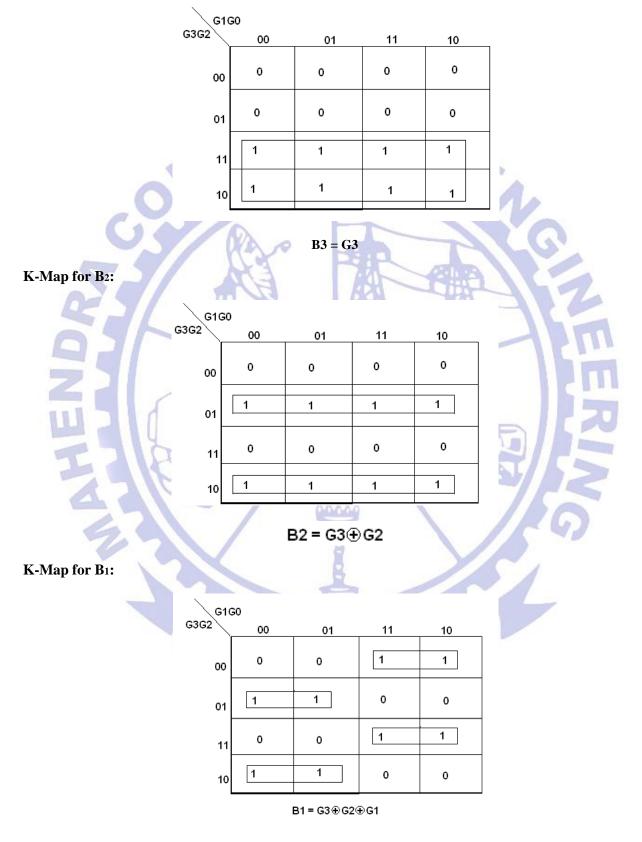

B2 = G3⊕G2

B3 = G3

J.SAMPATHKUMAR, AP/ECE

### K-Map for B3:

MAHENDRA COLLEGE OF ENGINEERING

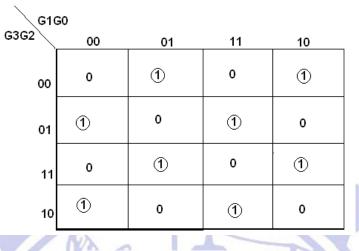

### K-Map for Bo:

B0 = G3⊕G2⊕G1⊕G0

### **TRUTH TABLE:**

| Y   | Gray | Code             |    | P m        | Binary | y Code     |            |

|-----|------|------------------|----|------------|--------|------------|------------|

| G3  | G2   | <b>G1</b>        | G0 | <b>B</b> 3 | B2     | <b>B</b> 1 | <b>B</b> 0 |

| 0   | 0    | 0                | 0  | 0          | 0      | 0          | 0          |

| 0   | 0    | 0                | 1/ | 0          | 0      | 0          | 1          |

| 0   | 0    | Ť                | 1  | 0          | 0      | 1          | 0          |

| 0   | 0    | MCE              | 0  | 0          | 70     | 1          | 21         |

| 0   | 1    |                  | 0  | 0          |        | 0          | 0          |

| 0   |      | LI               |    | 0          |        | 0          | 1          |

| 0   | _1   | 0                |    | 0          | T      |            | 0          |

| 0   | 1    | 0                | 0  | 0          | 1      | 1          | 1          |

| 1   | 1    | 0                | 0  | 1          | 0      | 0          | 0          |

| 1 🚬 | 71   | 0                | 1  | 1          | 0      | 0          | 1          |

| 1   |      | 1                | 1  | 1          | 0      | ~ 1        | 0          |

| 1   | 1    |                  | 0  | 1          | 0      | 1          | 1          |

| 1   | 0    | 1                | 0  |            | 1      | 0          | 0          |

| 1   | 0    | $\mathbf{R}_{1}$ | 1  | 1          |        | 0          | 1          |

| 1   | 0    | 200              | 1  | 1          | 1 000  | 1          | 0          |

| 1   | 0    | 00010            | 0  | 1          | CIDOT  | 1          | 1          |

தாய்மை

MAHENDRA COLLEGE OF ENGINEERING

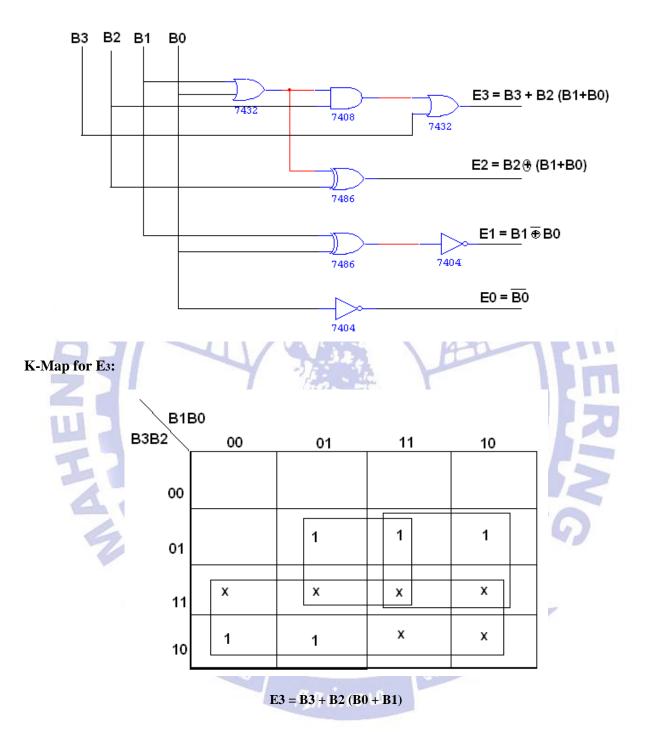

#### LOGIC DIAGRAM: BCD TO EXCESS-3 CONVERTOR

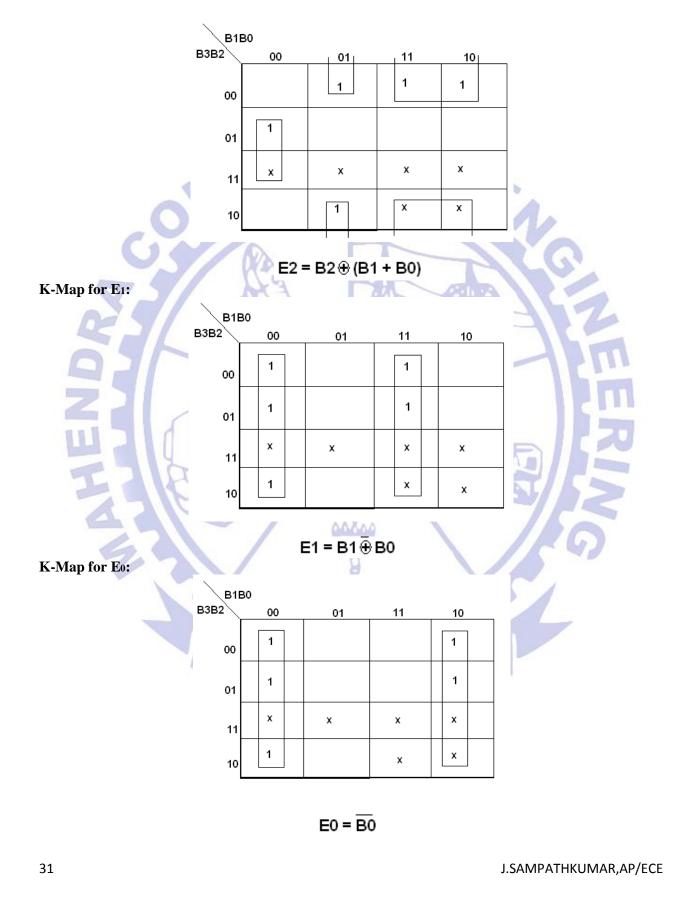

### K-Map for E2:

#### MAHENDRA COLLEGE OF ENGINEERING

#### **TRUTH TABLE:**

|           | BCD            | input      |           |    | Excess – | 3 output   |    |

|-----------|----------------|------------|-----------|----|----------|------------|----|

| <b>B3</b> | B2             | <b>B</b> 1 | <b>B0</b> | E3 | E2       | <b>E</b> 1 | EO |

| 0         | 0              | 0          | 0         | 0  | 0        | 1          | 1  |

| 0         | 0              | 0          | 1         | 0  | 1        | 0          | 0  |

| 0         | 0              | 1          | 0         | 0  | 1        | 0          | 1  |

| 0         | 0              | 1          | 1         | 0  | 1        | 1          | 0  |

| 0         | 1              | 0          | 0         | 0  | 1        | 1          | 1  |

| 0         | 1              | 0          | 1         |    | 0        | 0          | 0  |

| 0         | 1              | 1          | 0         | 1  | 0        | 0          | 1  |

| 0         | 1              | 1          | 1         | 1  | 0        | 1          | 0  |

| 1         | 0              | 0          | 0         | 1  | 0        | 1          | 1  |

| 1         | 0              | 0          | 1         | 1  | 1        | 0          | 0  |

| 1         | 0              |            | 0         | X  | X        | Х          | Х  |

| 1         | 0              | 1          | 1         | X  | X        | X          | X  |

| 1         |                | 0          | 0         | X  | X        | X          | X  |

| 1         |                | 0          | 21        | X  | Х        | X          | X  |

| 1         |                | 1          | 0         | X  | Х        | Х          | X  |

| 1         | $\overline{1}$ |            |           | X  | X        | X          | X  |

|           |                |            |           | 12 |          |            |    |

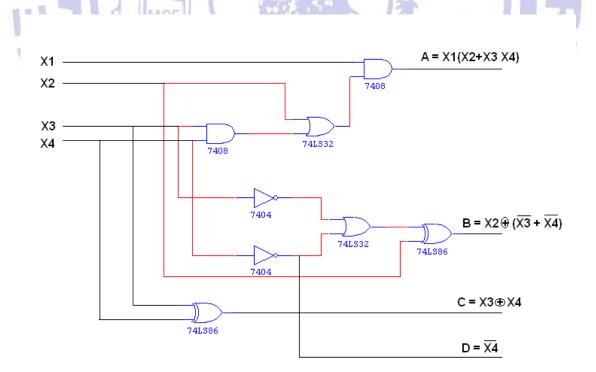

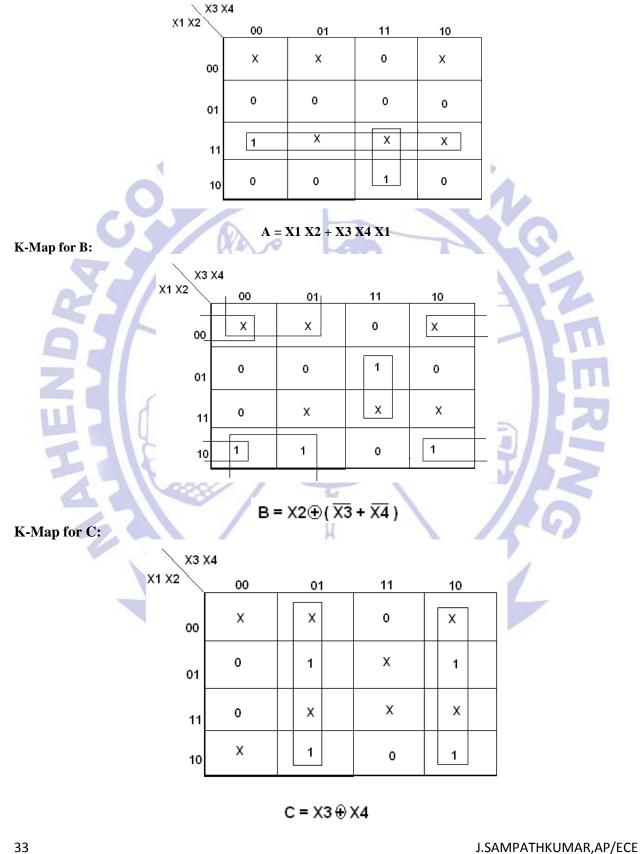

LOGIC DIAGRAM: EXCESS-3 TO BCD CONVERTOR

MAHENDRA COLLEGE OF ENGINEERING

#### K-Map for A:

MAHENDRA COLLEGE OF ENGINEERING

### K-Map for D:

# D = X4

#### **TRUTH TABLE:**

| 4         | Excess –   | 3 output    | 64.4      | 14        | BCD           | input 🛛 🔍 |            |

|-----------|------------|-------------|-----------|-----------|---------------|-----------|------------|

| <b>B3</b> | <b>B</b> 2 | B1          | <b>B0</b> | <b>B3</b> | <b>B2</b>     | <b>B1</b> | <b>B</b> 0 |

| 0         | 0          | mor 1       | 1         | 0         | 0             |           | 0          |

| 0         | 17         | 0           | 0         | 0         | 0             | 0         |            |

| 0         | 1          | 0           |           | -0        |               |           | 0          |

| 0         |            |             | 0         | 0         | 0             | 1         | 51         |

| 0         | 1          | 1           | 1 0       | 0         | 1             | 0         | 0          |

| 1 🚽       | 0          | 0           | 0         | 0         | 1             | 0         | 1          |

| 1         | 0          | 0           | 1         | 0         |               | 1         | 0          |

| 1         | 0          |             | 0         | 0         | 1             | 1         | 1          |

| 1         | 0          | 1           |           |           | 0             | 0         | 0          |

| 1         | 1          | 0           | 0         | 1         | 0             | 0         | 1          |

|           |            | entilements |           |           | Giding contra |           |            |

# **RESULT:**

Thus the code converters were designed and verified using the corresponding truth table.

#### EXP NO: 5

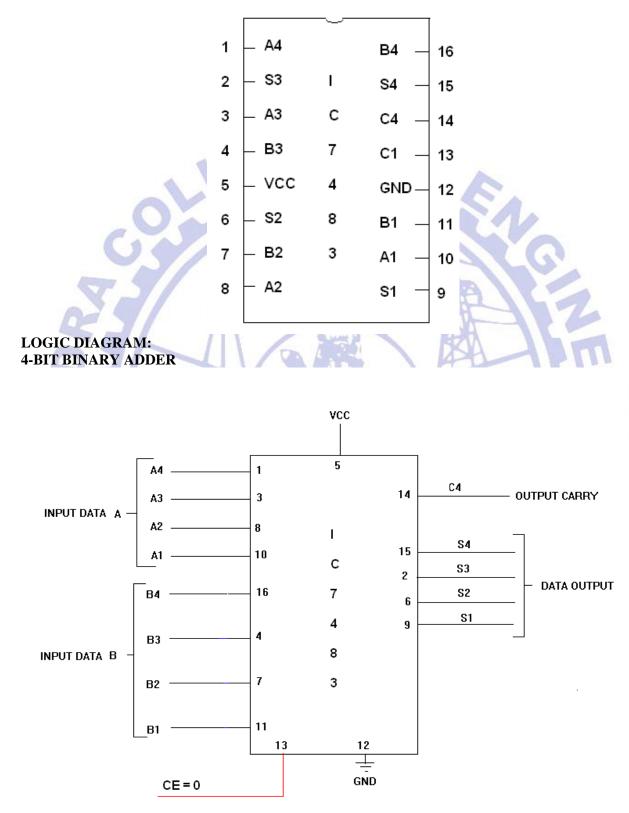

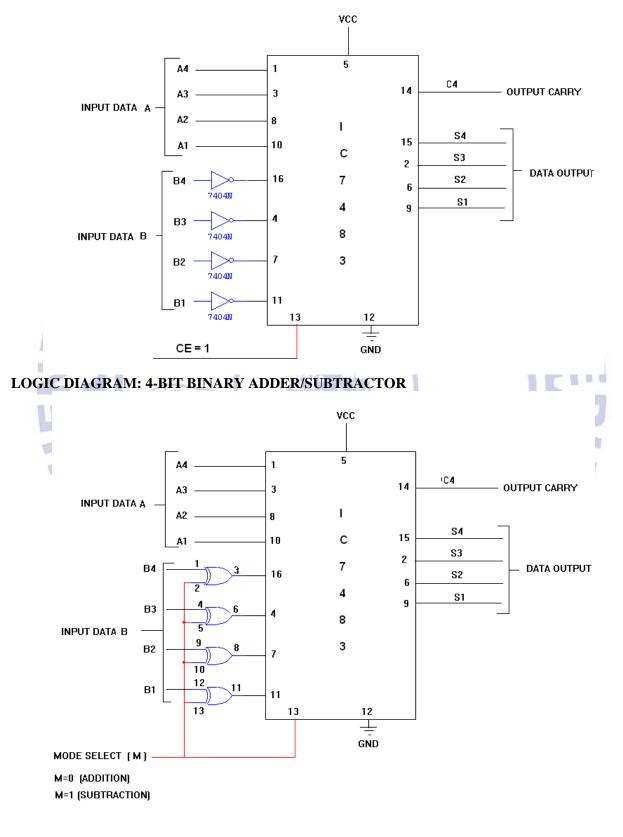

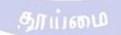

### **DESIGN OF 4-BIT ADDER AND SUBTRACTOR**

#### AIM:

To design and implement 4-bit adder and subtractor using IC 7483.

### **APPARATUS REQUIRED:**

| Sl.No. | COMPONENT      | SPECIFICATION | QTY. |

|--------|----------------|---------------|------|

| 1.     | IC             | IC 7483       | 1    |

| 2.     | EX-OR GATE     | IC 7486       | 1    |

| 3.     | NOT GATE       | IC 7404       | 1    |

| 3.     | IC TRAINER KIT |               | 1    |

| 4.     | PATCH CORDS    |               | 40   |

|        |                |               |      |

#### THEORY: 4 BIT BINARY ADDER:

A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers. It can be constructed with full adders connected in cascade, with the output carry from each full adder connected to the input carry of next full adder in chain. The augends bits of 'A' and the addend bits of 'B' are designated by subscript numbers from right to left, with subscript 0 denoting the least significant bits. The carries are connected in chain through the full adder. The input carry to the adder is C0 and it ripples through the full adder to the output carry C4.

### **4 BIT BINARY SUBTRACTOR:**

The circuit for subtracting A-B consists of an adder with inverters, placed between each data input 'B' and the corresponding input of full adder. The input carry C0 must be equal to 1 when performing subtraction.

### **4 BIT BINARY ADDER/SUBTRACTOR:**

The addition and subtraction operation can be combined into one circuit with one common binary adder. The mode input M controls the operation. When M=0, the circuit is adder circuit. When M=1, it becomes subtractor.

### **4 BIT BCD ADDER:**

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 19, the 1 in the sum being an input carry. The output of two decimal digits must be represented in BCD and should appear in the form listed in the columns. ABCD adder that adds 2 BCD digits and produce a sum digit in BCD. The 2 decimal digits, together with the input carry, are first added in the top 4 bit adder to produce the binary sum.

#### **PIN DIAGRAM FOR IC 7483:**

J.SAMPATHKUMAR, AP/ECE

#### LOGIC DIAGRAM: 4-BIT BINARY SUBTRACTOR

J.SAMPATHKUMAR, AP/ECE

#### DIGITAL LAB

### **TRUTH TABLE:**

| I  | nput ] | Data 🛛 | A  | I         | Input Data B |           |           |   | Addition  |           |           | Subtraction |   |    |    |    |           |

|----|--------|--------|----|-----------|--------------|-----------|-----------|---|-----------|-----------|-----------|-------------|---|----|----|----|-----------|

| A4 | A3     | A2     | A1 | <b>B4</b> | <b>B3</b>    | <b>B2</b> | <b>B1</b> | С | <b>S4</b> | <b>S3</b> | <b>S2</b> | <b>S1</b>   | В | D4 | D3 | D2 | <b>D1</b> |

| 1  | 0      | 0      | 0  | 0         | 0            | 1         | 0         | 0 | 1         | 0         | 1         | 0           | 1 | 0  | 1  | 1  | 0         |

| 1  | 0      | 0      | 0  | 1         | 0            | 0         | 0         | 1 | 0         | 0         | 0         | 0           | 1 | 0  | 0  | 0  | 0         |

| 0  | 0      | 1      | 0  | 1         | 0            | 0         | 0         | 0 | 1         | 0         | 1         | 0           | 0 | 1  | 0  | 1  | 0         |

| 0  | 0      | 0      | 1  | 0         | 1            | 1         | 1         | 0 | 1         | 0         | 0         | 0           | 0 | 1  | 0  | 1  | 0         |

| 1  | 0      | 1      | 0  | 1         | 0            | 1         | 1         | 1 | 0         | 0         | 1         | 0           | 0 | 1  | 1  | 1  | 1         |

| 1  | 1      | 1      | 0  | 1         | 1            | 1         | 1         | 1 | 1         | 0         | 1         | 0           | 0 | 1  | 1  | 1  | 1         |

| 1  | 0      | 1      | 0  | 1         | 1            | 0         | 1         | 1 | 0         | 1         | 4         | 1           | 0 | 1  | 1  | 0  | 1         |

# **RESULT:**

Thus the 4-BIT adder/subtractor using IC 7483 was implemented and output was verified with the help of truth table.

## EXP NO: 6 (a) ODD PARITY CHECKER /GENERATOR

#### AIM:

To design and verify the truth table of a three bit Odd Parity generator and checker.

# **APPARATUS REQUIRED**:

| S.No | Name of the Apparatus  | Range   | Quantity |

|------|------------------------|---------|----------|

| 1.   | Digital IC trainer kit |         | 1        |

| 2.   | EX-OR gate             | IC 7486 |          |

| 3.   | NOT gate               | IC 7404 |          |

| 4.   | Connecting wires       |         | required |

## **THEORY:**

A parity bit is used for the purpose of detecting errors during transmission of binary information. A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message including the parity bit is transmitted and then checked at the receiving end for errors.

An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker. In even parity the added parity bit will make the total number of 1's an even amount and in odd parity the added parity bit will make the total number of 1's an odd amount. In a three bit odd parity generator the three bits in the message together with the parity bit are transmitted to their destination, where they are applied to the parity checker circuit. The parity checker circuit checks for possible errors in the transmission.

Since the information was transmitted with odd parity the four bits received must have an odd number of 1's. An error occurs during the transmission if the four bits received have an even number of 1's, indicating that one bit has changed during transmission. The output of the parity checker is denoted by PEC (parity error check) and it will be equal to 1 if an error occurs, i.e., if the four bits received has an even number of 1's.

DIGITAL LAB

### **ODD PARITY GENERATOR TRUTH TABLE:**

| S.No | ( Three | INPU7<br>e bit m | OUTPUT<br>( Odd<br>Parity bit) |   |  |

|------|---------|------------------|--------------------------------|---|--|

|      | Α       | B                | С                              | P |  |

| 1.   | 0       | 0                | 0                              | 1 |  |

| 2.   | 0       | 0                | 1                              | 0 |  |

| 3.   | 0       | 1                | 0                              | 0 |  |

| 4.   | 0       | 1                | 1                              |   |  |

| 5.   | 1       | 0                | 0                              | 0 |  |

| 6.   | 61      | 0                |                                | 1 |  |

| 7.   | KA.     | 2 1              | 0                              | 1 |  |

| 8.   | A13     | 1                | 1                              | 0 |  |

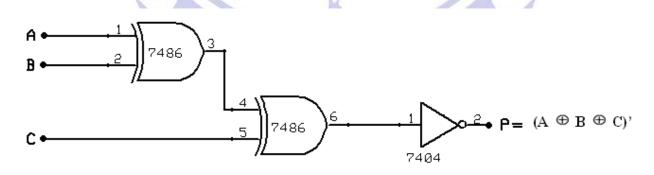

From the truth table the expression for the output parity bit is,

$$P(A, B, C) = \Sigma(0, 3, 5, 6)$$

Also written as, (Reduce using K-Map)

$$P = A'B'C' + A'BC + AB'C + ABC' = (A \oplus B \oplus C)$$

CIRCUIT DIAGRAM: ODD PARITY GENERATOR

#### DIGITAL LAB

### **ODD PARITY CHECKER TRUTH TABLE:**

|                  | S.No | ( four b |     | PUT<br>age Rece | OUTPUT<br>(Parity error<br>check) |   |    |

|------------------|------|----------|-----|-----------------|-----------------------------------|---|----|

|                  |      | Α        | В   | С               | Р                                 | X |    |

|                  | 1.   | 0        | 0   | 0               | 0                                 | 1 |    |

|                  | 2.   | 0        | 0   | 0               | 1                                 | 0 |    |

|                  | 3.   | 0        | 0   |                 | 0                                 | 0 | ]  |

|                  | 4.   | 0        | 0   | 1               | 1                                 |   |    |

|                  | 5.   | 0        | 1   | 0               | 0                                 | 0 |    |

| (                | 6.   | 0        | 1   | 0               | 1                                 |   |    |

|                  | 7.   | 0        |     |                 | 0                                 |   |    |

|                  | 8.   | 0        | HA. | 1               | 271                               |   |    |

| ~                | 9.   | 1        | 0   | 0               | 0                                 | 0 | 74 |

|                  | 10.  | 1        | 0   | 0               |                                   |   |    |

| 0                | 11.  | 1        | 0   | 1               | 0                                 |   |    |

|                  | 12.  | 1        | 0   | 1               | 1                                 | 0 |    |

| $\mathbb{Z}^{2}$ | 13.  | 1        | 1   | 0               | 0                                 | 1 |    |

|                  | 14.  | H        | 1   | 0               | 1                                 | 0 |    |

| ш                | 15.  | MCE      | 1   |                 | 0                                 | 0 |    |

|                  | 16.  | 14P      | 1   | 1               | 1                                 |   |    |

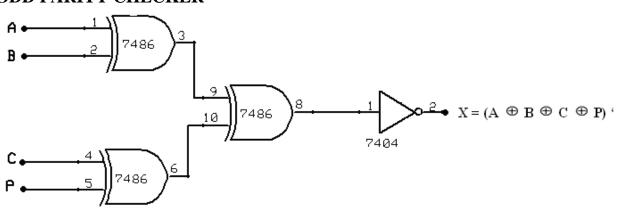

From the truth table the expression for the output parity checker bit is, X (A, B, C, P) =  $\Sigma$  (0, 3, 5, 6, 9, 10, 12, 15)

DIMILIONIN 1

The above expression is reduced as,

$X = (A \oplus B \oplus C \oplus P)$

เริ่มอย่างสาม

# CIRCUIT DIAGRAM: ODD PARITY CHECKER

# **PROCEDURE:**

- 1. Connections are given as per the circuit diagrams.

- 2. For all the ICs 7th pin is grounded and 14th pin is given +5 V supply.

- 3. Apply the inputs and verify the truth table for the Parity generator and checker.

### **RESULT:**

The design of the three bit odd Parity generator and checker circuits was done and their truth tables were verified.

DIGITAL LAB

# EXP NO: 6 (b) EVEN PARITY CHECKER /GENERATOR

### AIM:

To design and verify the truth table of a three bit Even Parity generator and checker.

# **APPARATUS REQUIRED**:

| S.No | Name of the Apparatus  | Range   | Quantity |

|------|------------------------|---------|----------|

| 1.   | Digital IC trainer kit | Sec.    | 1        |

| 2.   | EX-OR gate             | IC 7486 | 6        |

| 3.   | Connecting wires       | AUR     | required |

# **THEORY:**

An even parity bit generator generates an output of 0 if the number of 1's in the input sequence is even and 1 if the number of 1's in the input sequence is odd. The checker circuit gives an output of 0 if there is no error in the parity bit generated. Thus it basically checks to see if the parity bit generator is error free or not.

# **EVEN PARITY GENERATOR TRUTH TABLE:**

| S.No | /     | INPUI    | OUTPUT  |                       |

|------|-------|----------|---------|-----------------------|

|      | (Thre | ee bit m | essage) | ( Even<br>Parity bit) |

| an   | A     | В        | С       | Р                     |

| 1.   | 040   | 0        | 0       | 1 Gun O               |

| 2.   | 0     | 0        | 1       | 1                     |

| 3.   | 0     | 1        | 0       | 1                     |

| 4.   | 0     | 1        | 1       | 0                     |

MAHENDRA COLLEGE OF ENGINEERING

| 5. | 1 | 0 | 0 | 1 |  |

|----|---|---|---|---|--|

| 6. | 1 | 0 | 1 | 0 |  |

| 7. | 1 | 1 | 0 | 0 |  |

| 8. | 1 | 1 | 1 | 1 |  |

|    |   |   |   |   |  |

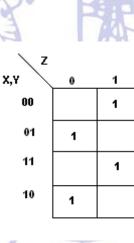

The circuit can now be derived by drawing the K-map for the output.

From this the minimal output equation is

$P = \overline{X}\overline{Y}Z + \overline{X}\overline{Y}\overline{Z} + X\overline{Y}Z + X\overline{Y}\overline{Z} = X \oplus Y \oplus Z$

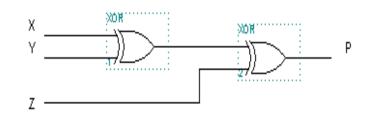

This function can be implemented using exclusive-or gates. The schematic of the parity generator circuit is shown in Figure 1.

Figure 1: Parity bit generator

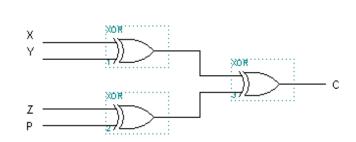

Similarly the checker circuit can be designed using XOR gates, where  $C = X \oplus Y \oplus Z \oplus P$  and the circuit is shown in Figure 2.

## EVEN PARITY CHECKER TRUTH TABLE:

- 2. For all the ICs 7th pin is grounded and 14th pin is given +5 V supply.

- 3. Apply the inputs and verify the truth table for the Parity generator and checker.

## **RESULT:**

The design of the three bit even Parity generator and checker circuits was done and their truth tables were verified.

#### DIGITAL LAB

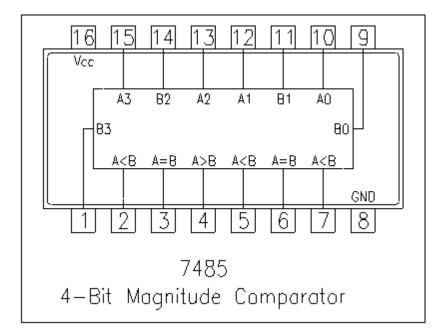

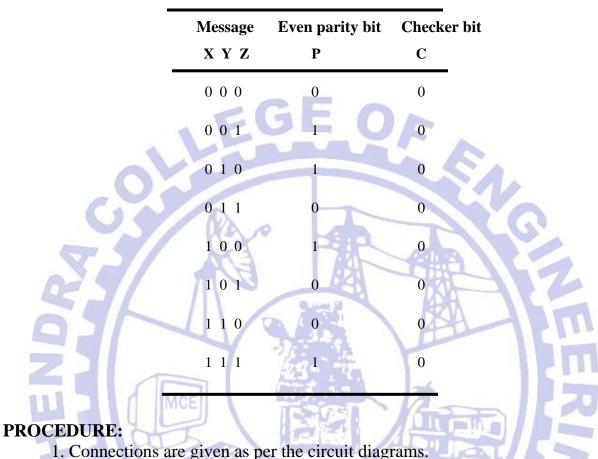

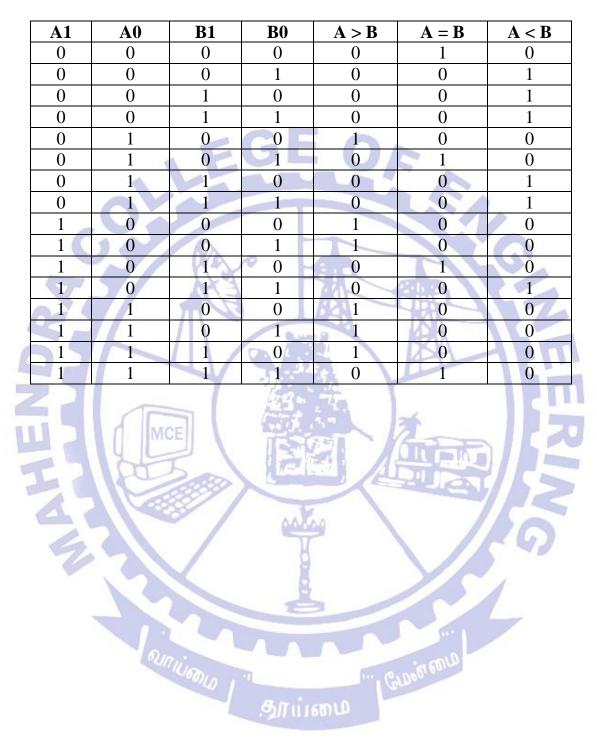

# EXP NO: 7 DESIGN AND IMPLEMENTATION OF MAGNITUDE COMPARATOR

#### AIM:

To design and implement

- (i) 2 bit magnitude comparator using basic gates.

- (ii) 8 bit magnitude comparator using IC 7485.

# **APPARATUS REQUIRED:**

| Sl.No. | COMPONENT       | SPECIFICATION | QTY.     |

|--------|-----------------|---------------|----------|

| 1.     | AND GATE        | IC 7408       | 2        |

| 2.     | X-OR GATE       | IC 7486       |          |

| 3.     | OR GATE         | IC 7432       |          |

| 4.     | NOT GATE        | IC 7404       | 1        |

| 5.     | 4-BIT MAGNITUDE | IC 7485       | 2        |

|        | COMPARATOR      |               |          |

| 6.     | IC TRAINER KIT  | A RA          | 1        |

| 7.     | PATCH CORDS     |               | required |

## **THEORY:**

The comparison of two numbers is an operator that determine one number is greater than, less than (or) equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determine their relative magnitude. The outcome of the comparator is specified by three binary variables that indicate whether A>B, A=B (or) A<B.

$$A = A3 A2 A1 A0$$

$$B = B3 B2 B1 B0$$

The equality of the two numbers and B is displayed in a combinational circuit designated by the symbol (A=B).

This indicates A greater than B, then inspect the relative magnitude of pairs of significant digits starting from most significant position. A is 0 and that of B is 0.

We have A<B, the sequential comparison can be expanded as

$A > B = A3B3^{1} + X3A2B2^{1} + X3X2A1B1^{1} + X3X2X1A0B0^{1}$

$A < B = A3^{1}B3 + X3A2^{1}B2 + X3X2A1^{1}B1 + X3X2X1A0^{1}B0$

The same circuit can be used to compare the relative magnitude of two BCD digits. Where,

DIGITAL LAB

A = B is expanded as,

$$\hat{A} = B = (A3 + B3) (A2 + B2) (A1 + B1) (A0 + B0)$$

$\psi$   $\psi$   $\psi$   $\psi$

$x3$   $x2$   $x1$   $x0$

## **PROCEDURE:**

- (i) Connections are given as per circuit diagram.

- (ii) Logical inputs are given as per circuit diagram.

- (iii) Observe the output and verify the truth table.

# **LOGIC DIAGRAM: 2 BIT MAGNITUDE COMPARATOR**

MAHENDRA COLLEGE OF ENGINEERING

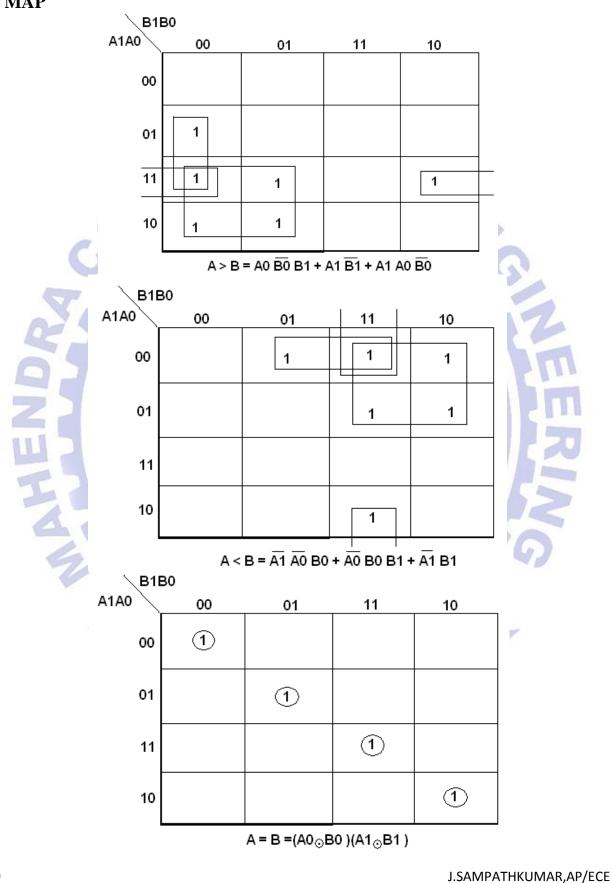

## K MAP

#### **TRUTH TABLE**

J.SAMPATHKUMAR,AP/ECE

#### **PIN DIAGRAM FOR IC 7485:**

| Α    | В    | A>B         | A=B | A <b< th=""></b<> |

|------|------|-------------|-----|-------------------|

| 0000 | 0000 | 9// () 60 U | 1   | 0                 |

| 0000 | 0000 |             |     |                   |

| 0001 | 0001 | 1           | 0   | 0                 |

| 0000 | 0000 |             |     |                   |

| 0000 | 0000 | 0           | 0   | 1                 |

| 0001 | 0001 |             |     |                   |

J.SAMPATHKUMAR, AP/ECE

# **RESULT:**

Thus the 2-bit and 8-bit magnitude comparator was designed and verified using the logic gates.

#### DIGITAL LAB

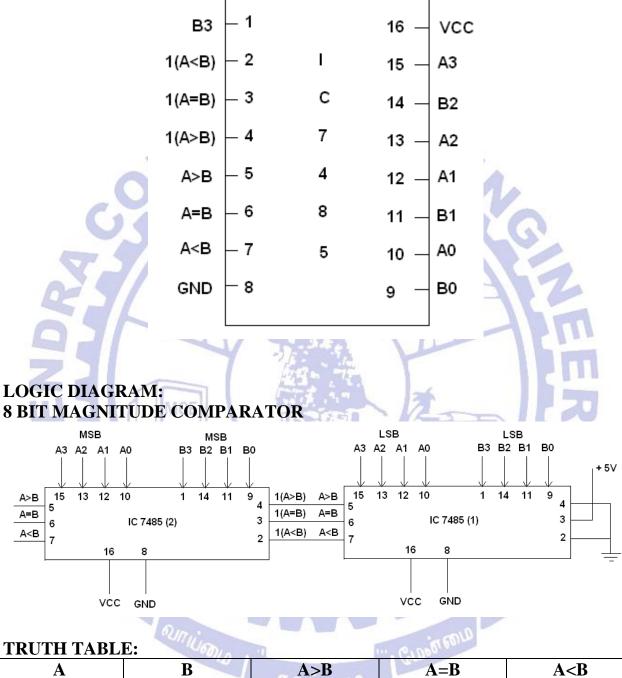

# EXP NO: 8 DESIGN AND IMPLEMENTATION OF MULTIPLEXER AND DEMULTIPLEXER

### AIM:

To design and implement Multiplexer and Demultiplexer using logic gates.

| APPAR | ATUS | <b>REQUIRED:</b> |   |

|-------|------|------------------|---|

|       |      |                  | _ |

| Sl. | COMPONENTS          | SPECIFICATION/    | Qty  |

|-----|---------------------|-------------------|------|

| No. |                     | RANGE             |      |

| 1.  | 3 I/P AND GATE (or) | IC 7411 / IC 7408 | 2    |

|     | 2I/p                |                   | S    |

| 2.  | OR GATE             | IC 7432           | 1    |

| 3.  | NOT GATE            | IC 7404           |      |

| 4.  | DIGITAL TRAINER     |                   | 1    |

| 57  | KIT                 | ALL ALL           |      |

| 5.  | CONNECTING          |                   | Req. |

| K D | WIRES               |                   |      |

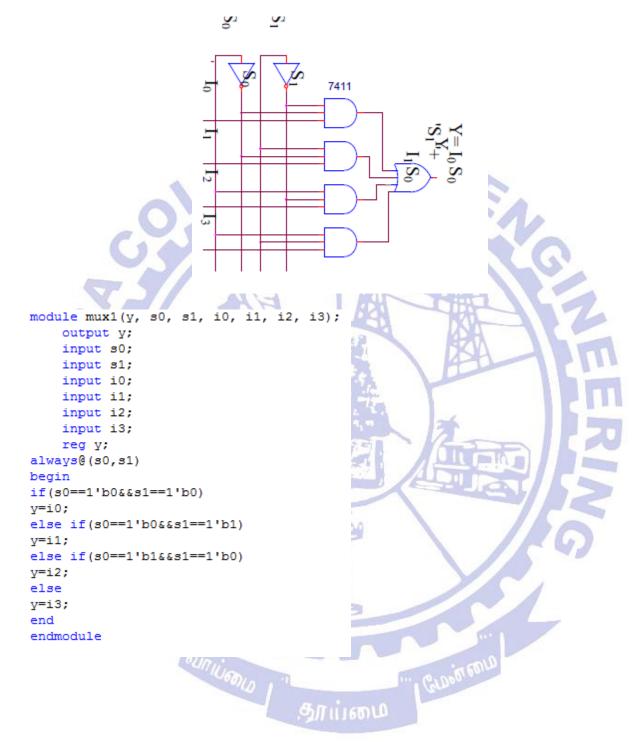

## THEORY: MULTIPLEXER:

Multiplexer means transmitting a large number of information units over a smaller number of channels or lines. A digital multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally there are  $2_n$  input line and n selection lines whose bit combination determine which input is selected.

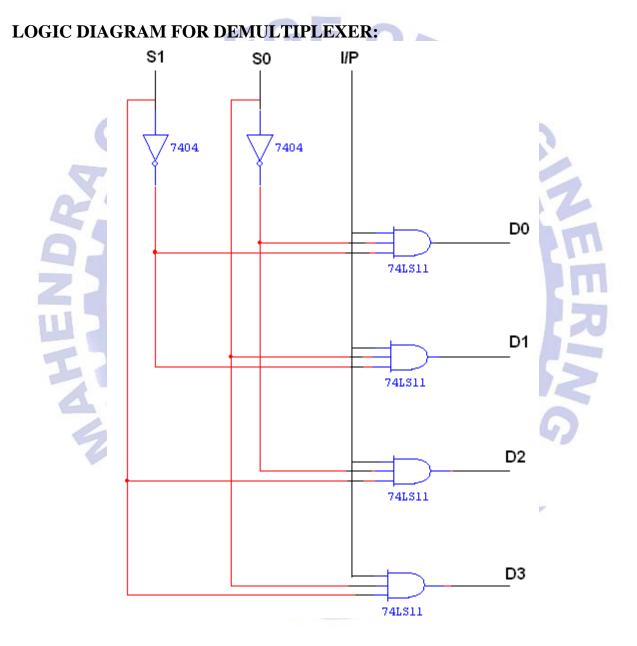

### **DEMULTIPLEXER:**

The function of Demultiplexer is in contrast to multiplexer function. It takes information from one line and distributes it to a given number of output lines. For this reason, the demultiplexer is also known as a data distributor. Decoder can also be used as demultiplexer. In the 1: 4 demultiplexer circuit, the data input line goes to all of the AND gates. The data select lines enable only one gate at a time and the data on the data input line will pass through the selected gate to the associated data output line.

### **BLOCK DIAGRAM FOR 4:1 MULTIPLEXER:**

MAHENDRA COLLEGE OF ENGINEERING

#### **FUNCTION TABLE:**

| <b>S1</b> | <b>S0</b> | <b>INPUTS (Y)-output</b>      |

|-----------|-----------|-------------------------------|

| 0         | 0         | $D0 \rightarrow D0 S1' S0'$   |

| 0         | 1         | $D1 \rightarrow D1 S1' S0$    |

| 1         | 0         | $D2 \rightarrow D2 S1 S0'$    |

| 1         | 1         | $D3 \rightarrow D3 \ S1 \ S0$ |

# Y = D0 S1' S0' + D1 S1' S0 + D2 S1 S0' + D3 S1 S0

## **TRUTH TABLE:**

|   |           | and the second |            |

|---|-----------|------------------------------------------------------------------------------------------------------------------|------------|

| 2 | <b>S1</b> | <b>S0</b>                                                                                                        | Y = OUTPUT |

| 5 | 0         | 0                                                                                                                | D0         |

| 6 | 0         | 1                                                                                                                | D1         |

|   | 1         | 0                                                                                                                | D2         |

|   | 1         | 1                                                                                                                | D3         |

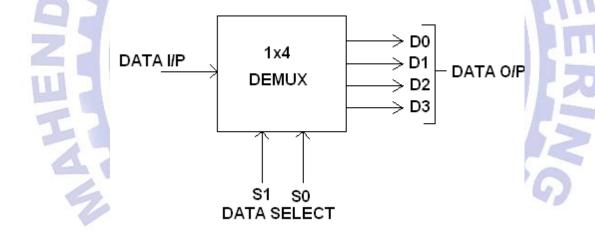

# **BLOCK DIAGRAM FOR 1:4 DEMULTIPLEXER:**

| FUNCTION TABL | Æ:        |            | 2                              |

|---------------|-----------|------------|--------------------------------|

|               | <b>S1</b> | <b>S0</b>  | INPUT                          |

|               | 0         | 0          | $X \rightarrow D0 = X S1' S0'$ |

|               | 20        | 1          | $X \rightarrow D1 = X S1' S0$  |

|               | 1         | <b>W 0</b> | $X \rightarrow D2 = X S1 S0'$  |

|               | 1         | 1          | $X \rightarrow D3 = X S1 S0$   |

Y = X S1' S0' + X S1' S0 + X S1 S0' + X S1 S0

DIGITAL LAB

# **PROCEDURE:**

(i) Connections are given as per circuit diagram.

(ii) Logical inputs are given as per circuit diagram.

(iii) Observe the output and verify the truth table.

#### DIGITAL LAB

## **TRUTH TABLE:**

| INPUT |           |           | OUTPUT    |    |    |    |

|-------|-----------|-----------|-----------|----|----|----|

| I/P   | <b>S1</b> | <b>S0</b> | <b>D0</b> | D1 | D2 | D3 |

| 0     | 0         | 0         | 0         | 0  | 0  | 0  |

| 0     | 0         | 1         | 1         | 0  | 0  | 0  |

| 0     | 1         | 0         | 0         | 0  | 0  | 0  |

| 0     | 1         |           | 0         | 1  | 0  | 0  |

| 1     | 0         | 0         | 0         | 0  | 0  | 0  |

| 1     | 0         | 1         | 0         | 0  | 1  | 0  |

| 1     | I         | 0         | 0         | 0  | 0  | 0  |

|       | 1         | 1         | 0         | 0  | 0  | 1  |

### **Result:**

Thus the 4:1 Multiplexer and 1:4 Demultiplexer were designed using logic gates and truth table were verified.

United 1

Gibinmu

#### DIGITAL LAB

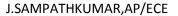

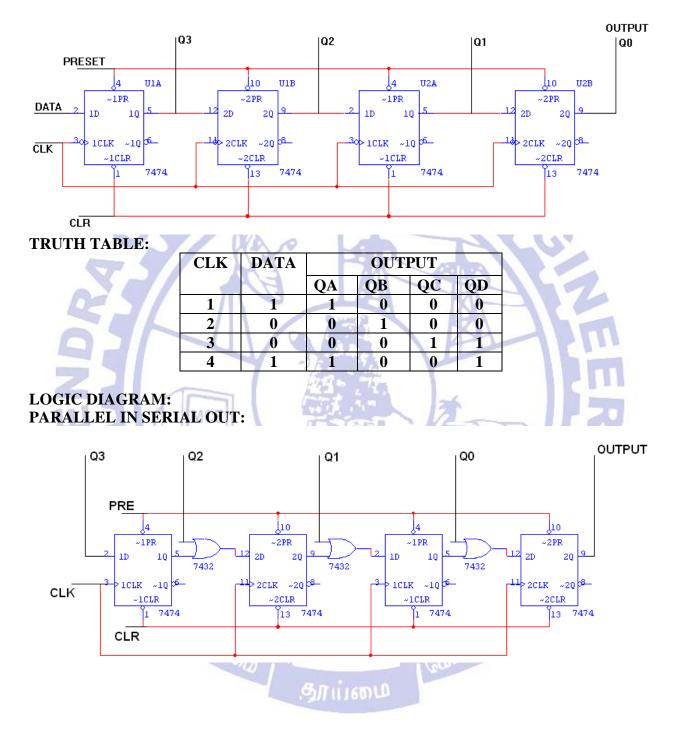

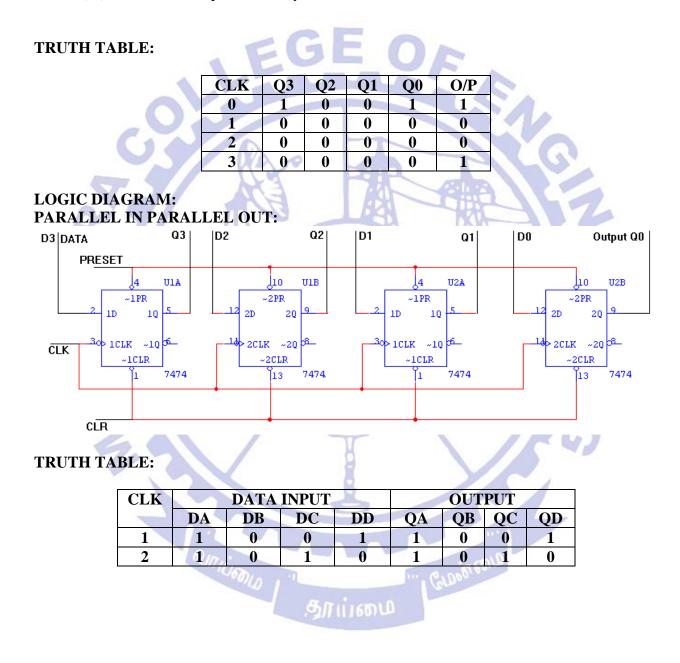

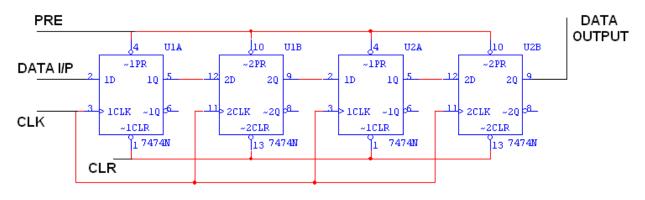

## EXP NO: 09 DESIGN AND IMPLEMENTATION OF SHIFT REGISTER

## AIM:

To design and implement

- (i) Serial in serial out

- (ii) Serial in parallel out

- (iii) Parallel in serial out

- (iv) Parallel in parallel out

## **APPARATUS REQUIRED:**

| Sl. No. | COMPONENTS             | SPECIFICATION/<br>RANGE | Qty  |

|---------|------------------------|-------------------------|------|

| 1.      | D- FLIP FLOP           | IC 7474                 | 2    |

| 2.      | OR GATE                | IC 7432                 | 1    |

| 3.      | DIGITAL TRAINER<br>KIT |                         |      |

| 4.      | CONNECTING             | and a                   | Req. |

|         | WIRES                  |                         | X    |

## **THEORY:**

A register is capable of shifting its binary information in one or both directions is known as shift register. The logical configuration of shift register consist of a D-Flip flop cascaded with output of one flip flop connected to input of next flip flop. All flip flops receive common clock pulses which causes the shift in the output of the flip flop. The simplest possible shift register is one that uses only flip flop. The output of a given flip flop is connected to the input of next flip flop of the register. Each clock pulse shifts the content of register one bit position to right.

## **PIN DIAGRAM:**

|                |     |   |      |            | 1  |

|----------------|-----|---|------|------------|----|

|                |     |   |      |            | r  |

| CLR0           | _ 1 | I | 14 — | vcc        |    |

| D0             | - 2 | С | 13 — | CLR1       |    |

| CLK0           | _ 3 | 7 | 12 — | D1         | 00 |

| PRE0           | _ 4 | 4 | 11 — | CLK1       |    |

| S0             | _ 5 | 7 | 10 — | PRE1       |    |

| <del>s</del> o | _ 6 | 4 | 9 —  | Q1         |    |

| GND            | - 7 | - | 8 —  | <u>Q</u> 1 |    |

|                |     |   |      |            |    |

#### J.SAMPATHKUMAR, AP/ECE

MAHENDRA COLLEGE OF ENGINEERING

## LOGIC DIAGRAM: SERIAL IN PARALLEL OUT:

## DIGITAL LAB

#### **PROCEDURE:**

(i) Connections are given as per circuit diagram.

- (ii) Logical inputs are given as per circuit diagram.

- (iii) Observe the output and verify the truth table.

## **LOGIC DIAGRAM: SERIAL IN SERIAL OUT:**

| TRUTH TABLE: |      | _         |        |      |     |

|--------------|------|-----------|--------|------|-----|

|              | CLK  | SERIAL IN | SERIAL |      | 5   |

|              | 100  |           | OUT    |      |     |

|              | 1    |           | 0      |      |     |

|              | 2    |           | 0      |      | 174 |

|              | 3    | 0         |        |      |     |

|              | 4    | D 1       | 1      | 4    |     |

|              | 5    | X         | 0      |      |     |

|              | 6    | X         | 0      |      |     |

|              | 7    | X         | 1      | 1    |     |

|              | E    | 46 P. 1 1 |        | ,    |     |

|              |      |           |        |      |     |

|              | K V  |           |        | -in- |     |

|              | 1000 |           |        | AL   |     |

|              | 21   |           |        |      |     |

|              | 0    | 00000     |        |      |     |

|              |      | T         |        |      | 6)  |

| DECIUT.      |      | - M       |        |      |     |

## **RESULT:**

Thus the implementation of shift registers using flip flops was completed successfully. ··· | Giasin ema

வாய்யை "தாய்பை

#### DIGITAL LAB

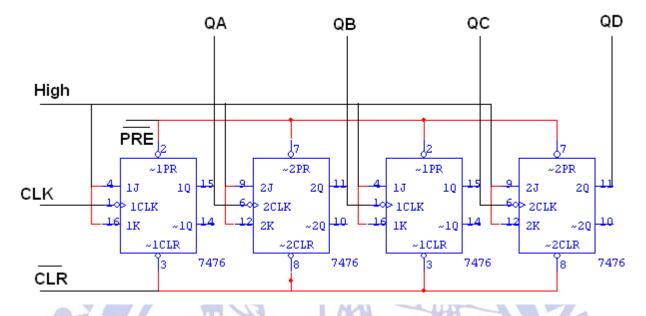

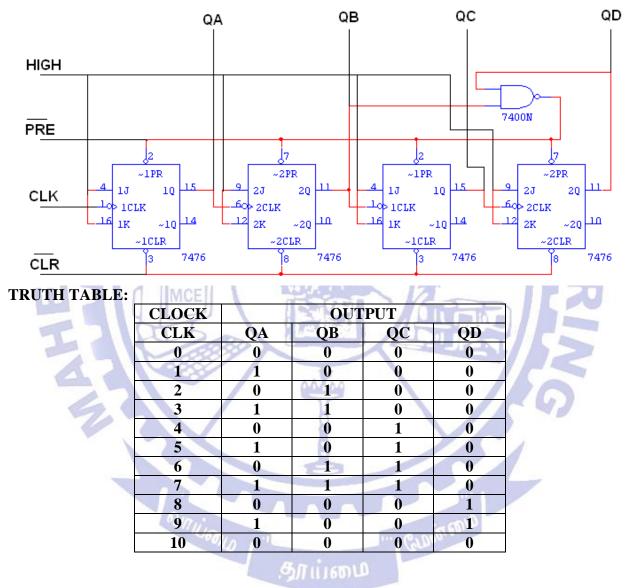

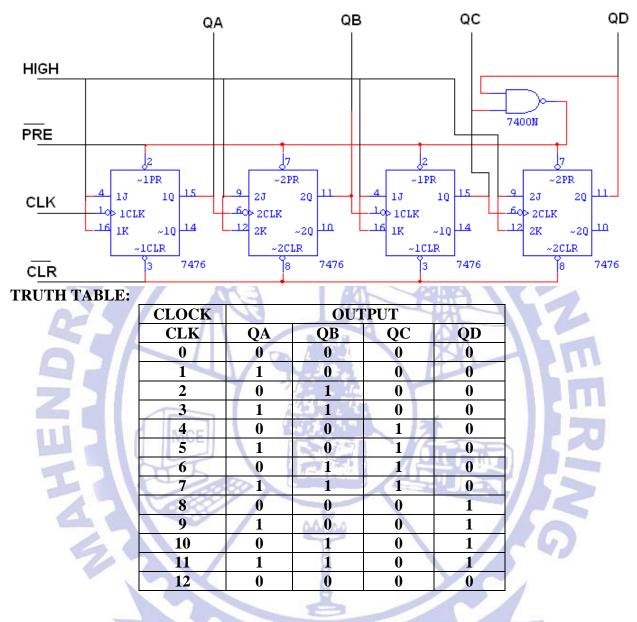

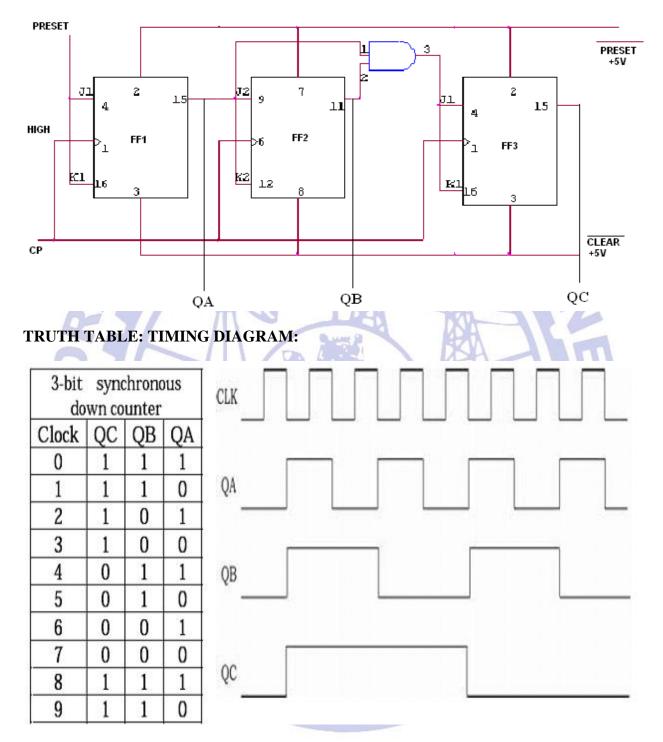

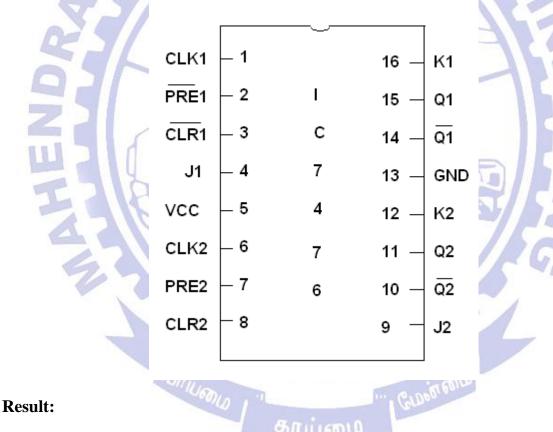

## EXP NO: 10 DESIGN AND IMPLEMENTATION OF ASYNCHRONOUS / RIPPLE COUNTER USING IC 7476

## AIM:

To design and implementation of 4 bit Asynchronous/Ripple counter, MOD 10 and MOD 12 Asynchronous/Ripple counter.

## **APPARATUS REQUIRED:**

| Sl. No. | COMPONENTS             | SPECIFICATION/<br>RANGE | Qty  |

|---------|------------------------|-------------------------|------|

| 1.      | JK FLIP FLOP           | IC 7476                 | 2    |

| 2.      | NAND GATE              | IC 7400                 | 1    |

| 3.      | DIGITAL TRAINER<br>KIT | I                       | 1    |

| 4.      | CONNECTING<br>WIRES    |                         | Req. |

## **THEORY:**

A counter is a register capable of counting number of clock pulse arriving at its clock input. Counter represents the number of clock pulses arrived. A specified sequence of states appears as counter output. This is the main difference between a register and a counter. There are two types of counter, synchronous and asynchronous. In synchronous common clock is given to all flip flop and in asynchronous first flip flop is clocked by external pulse and then each successive flip flop is clocked by Q or Q output of previous stage. A soon the clock of second stage is triggered by output of first stage. Because of inherent propagation delay time all flip flops are not activated at same time which results in asynchronous operation.

## PIN DIAGRAM FOR IC 7476:

| CLK1 | _ 1 |   | 16 — K1  |   |

|------|-----|---|----------|---|

| PRE1 | - 2 | I | 15 — Q1  | ~ |

| CLR1 | _ 3 | С | 14 — Q1  | Į |

| J1   | - 4 | 7 | 13 — GND |   |

| vcc  | _ 5 | 4 | 12 — K2  |   |

| CLK2 | - 6 | 7 | 11 — Q2  |   |

| PRE2 | - 7 | 6 | 10 — Q2  |   |

| CLR2 | - 8 |   | 9 — J2   |   |

|      |     |   |          |   |

MAHENDRA COLLEGE OF ENGINEERING

## LOGIC DIAGRAM FOR 4 BIT RIPPLE COUNTER:

|             | <i>n</i> n |                |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |   |

|-------------|------------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|

| TRUTH TABLE | C:         |                | B un S |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A     |   |

|             | CLOCK      |                | OUT    | 'PUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SA    |   |

|             | CLK        | QA             | QB     | QC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | QD    |   |

|             | 0          | 0              | 0      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0     |   |