# **CS 1202**

# Digital Principles & System Design

nal

1.Define the term digital.

The term digital refers to any process that is accomplished using discrete units

#### 2. What is meant by bit?

A binary digit is called bit

#### 3. What is the best example of digital system?

Digital computer is the best example of a digital system.

#### 4.Define byte?

A group of 8 bits.

#### 5.List the number systems?

- Decimal Number system

- ii) Binary Number system

- iii) Octal Number system

- iv) Hexadecimal Number system

6.State the sequence of operator precedence in Boolean expression?

- i) Parenthesis

- ii) AND

- iii) OR

#### 7. What is the abbreviation of ASCII and EBCDIC code?

ASCII- American Standard Code for Information Interchange. EBCDIC- Extended Binary Coded Decimal Information Code.

8.What are the universal gates? NAND and NOR

9. What are the different types of number complements?

i) r's Complement

ii) (r-1)'s Complement.

#### 10.Why complementing a number representation is needed?

Complementing a number becomes as in digital computer for simplifying the subtraction operation and for logical manipulation complements are used.

11. How to represent a positive and negative sign in computers?

Positive (+) sign by 0 Negative (-) sign by 1.

#### 12. What is meant by Map method?

The map method provides a simple straightforward procedure for minimizing Boolean function.

#### 13.What is meant by two variable map?

Two variable map have four minterms for two variables, hence the map consists of four squares, one for each minterm

#### 14. What is meant by three variable map?

Three variable map have 8 minterms for three variables, hence the map consists of 8 squares, one for each minterm

15.Which gate is equal to AND-inverter Gate? NAND gate.

16.Which gate is equal to OR-inverter Gate?

Rubbled OR gate is equal to------NAND gate

18. Bubbled AND gate is equal to-----NOR gate

#### 19. What is the use of Don't care conditions?

Any digital circuit using this code operates under the assumption that these unused combinations will never occur as long as the system

20.Express the function f(x, y, z)=1 in the sum of minterms and a product of maxterms? Minterms= $\Sigma(0,1,2,3,4,5,6,7)$ Maxterms=Nomaxterms.

21.What is the algebraic function of Exclusive-OR gate and Exclusive-NOR gate? F=xy<sup>1</sup> +  $x^{1}y$

$F=xy+x^1y^1$

- 22. What are the methods adopted to reduce Boolean function?

- i) Karnaugh map

- ii) Tabular method or Quine mccluskey method

- iii) Variable entered map technique.

#### 23. Why we go in for tabulation method?

This method can be applied to problems with many variables and has the advantage of being suitable for machine computation.

#### 24.State the limitations of karnaugh map.

i) Generally it is limited to six variable map (i.e.) more then six variable involving expressions are not reduced.

11.cor

ii) The map method is restricted in its capability since they are useful for simplifying only Boolean expression represented in standard form.

#### 25.What is tabulation method?

A method involving an exhaustive tabular search method for the minimum expression to solve a Boolean equation is called as a tabulation method.

#### 26.What are prime-implicants

The terms remained unchecked are called prime-implicants. They cannot be reduced further.

#### 27.Explain or Intone the advantages and disadvantages of K-map method?

The advantages of the K-map method are

- i. It is a fast method for simplifying expression up to four variables.

- ii. It gives a visual method of logic simplification.

- iii. Prime implicants and essential prime implicants are identified fast.

- iv. Suitable for both SOP and POS forms of reduction.

- v. It is more suitable for class room teachings on logic simplification.

The disadvantages of the K-map method are

- i. It is not suitable for computer reduction.

- ii. K-maps are not suitable when the number of variables involved exceed four.

- iii. Care must be taken to fill in every cell with the relevant entry, such as a 0, 1 (or) don't care terms.

#### 28.List out the advantages and disadvantages of Quine-Mc Cluskey method?

The advantages are,

- a. This is suitable when the number of variables exceed four.

- b. Digital computers can be used to obtain the solution fast.

- c. Essential prime implicants, which are not evident in K-map, can be clearly seen in the final results.

The disadvantages are,

- a. Lengthy procedure than K-map.

- b. Requires several grouping and steps as compared to K-map.

- c. It is much slower.

- d. No visual identification of reduction process.

- , y a composition of the second secon e. The Quine Mc Cluskey method is essentially a computer reduction

# UNIT II

#### 1.Define Positive Logic.

When high voltage or more positive voltage level is associated with binary '1' and while the low or less positive level is associated with binary '0' then the system adhering to this is called positive logic.

#### 2.Define Negative Logic.

When high voltage level is associated with binary '0' and while the low level is associated with binary '1' then the system adhering to this is called negative logic

#### 3 .List the characteristics of digital Ics

- i) propagation delay

- ii) power dissipation

- iii) Fan-in

- iv) Fan-out

- v) Noise margin

#### 4 .What is propagation delay?

It is the average transition delay time for the signal to propagate from input to output when the signals change in value.

reilli

#### 5.What is Noise margin?

It is the limit of a noise voltage, which may be present with out impairing the proper operation of the circuit.

#### 6. What is power dissipation?

It is the power consumed by the gate, which must be available from the power supply.

#### 7.Why parity checker is needed?

Parity checker is required at the receiver side to check whether the expected parity is equal to the calculated parity or not. If they are not equal then it is found that the received data has error.

#### 8. What is meant by parity bit?

Parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message, including the parity bit is transmitted and then checked at the receiving and for errors.

#### 9. Why parity generator necessary?

Parity generator is essential to generate parity bit in the transmitter.

#### 10.What is IC?

An integrated circuit is a small silicon semiconductor crystal called a chip containing electrical components such as transistors, diodes, resistors and capacitors. The various components are interconnected inside the chip to form an electronic circuit.

#### 11What are the needs for binary codes?

- a. Code is used to represent letters, numbers and punctuation marks.

- b. Coding is required for maximum efficiency in single transmission.

- c. Binary codes are the major components in the synthesis (artificial generation) of speech and video signals.

- d. By using error detecting codes, errors generated in signal transmission can be detected.

- e. Codes are used for data compression by which large amounts of data are transmitted in very short duration of time.

#### 12.Mention the different type of binary codes?

The various types of binary codes are,

- f. BCD code (Binary Coded decimal).

- g. Self-complementing code.

- h. The excess-3 (X's-3) code.

- i. Gray code.

- j. Binary weighted code.

- k. Alphanumeric code.

- 1. The ASCII code.

- m. Extended binary-coded decimal interchange code (EBCDIC).

- n. Error-detecting and error-correcting code.

- o. Hamming code.

#### 13.List the advantages and disadvantages of BCD code?

The advantages of BCD code are

- a. Any large decimal number can be easily converted into corresponding binary number

- b. A person needs to remember only the binary equivalents of decimal number from 0 to 9.

- c. Conversion from BCD into decimal is also very easy.

The disadvantages of BCD code are

- a. The code is least efficient. It requires several symbols to represent even small numbers.

- b. Binary addition and subtraction can lead to wrong answer.

- c. Special codes are required for arithmetic operations.

- d. This is not a self-complementing code.

- e. Conversion into other coding schemes requires special methods.

#### 14. What is meant by self-complementing code?

A self-complementing code is the one in which the members of the number system complement on themselves. This requires the following two conditions to be satisfied.

- a. The complement of the number should be obtained from that number by replacing 1s with 0s and 0s with 1s.

- b. The sum of the number and its complement should be equal to decimal 9. Example of a self-complementing code is

- i. 2-4-2-1 code.

- ii. Excess-3 code.

#### 15.Mention the advantages of ASCII code?

The following are the advantages of ASCII code

- a. There are  $2^7 = 128$  possible combinations. Hence, a large number of symbols, alphabets etc.., can be easily represented.

- b. There is a definite order in which the alphabets, etc.., are assigned to each code word.

- c. The parity bits can be added for error-detection and correction.

#### 16. What are the disadvantages of ASCII code?

The disadvantages of ASCII code are

- a. The length of the code is larger and hence more bandwidth is required for transmission.

- b. With more characters and symbols to represent, this is not completely sufficient.

#### 17.What is the truth table?

A truth table lists all possible combinations of inputs and the corresponding outputs.

#### 18.Define figure of merit?

Figure of merits is defined as the product of speed and power. The speed is specified in terms of propagation delay time expressed in nano seconds.

Figure of merits=Propagation delay time (ns)\*

Power (mw)

It is specified in pico joules (ns\*mw=PJ).

19. What are the two types of logic circuits for digital systems?

Combinational and sequential

#### 20.Define Combinational circuit.

A combinational circuit consist of logic gates whose outputs at anytime are determined directly from the present combination of inputs without regard to previous inputs.

#### 21.Define sequential circuits.

Their outputs are a function of the inputs and the state of memory elements. The state of memory elements, in turn, is a function of previous inputs.

#### 22. What is a half-adder?

The combinational circuit that performs the addition of two bits are called a half-adder.

#### 23.What is a full-adder?

The combinational circuit that performs the addition of three bits are called a half-adder.

#### 24. What is half-subtractor?

The combinational circuit that performs the subtraction of two bits are called a half-sub tractor.

#### 25.What is a full-subtractor?

The combinational circuit that performs the subtraction of three bits are called a half- sub tractor.

#### 26. What is Binary parallel adder?

A binary parallel adder is a digital function that produces the arithemetic sum of two binary numbers in parallel.

, minuters in parallel.

## UNIT III

#### 1.What is BCD adder?

A BCD adder is a circuit that adds two BCD digits in parallel and produces a sum digit also in BCD.

#### 2. What is Magnitude Comparator?

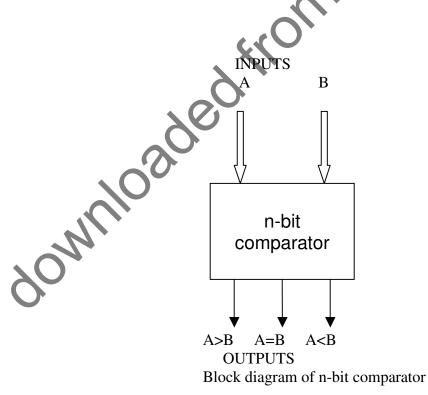

A Magnitude Comparator is a combinational circuit that compares two numbers, A and B and determines their relative magnitudes.

#### 3.What is decoder?

A decoder is a combinational circuit that converts binary information from 'n' input lines to a maximum of  $2^n$  unique output lines.

#### 4. What is encoder?

A decoder is a combinational circuit that converts binary information from  $2^{n}$ Input lines to a maximum of 'n' unique output lines.

#### 5.Define Multiplexing?

Multiplexing means transmitting a large number of information units over a smaller number of channels or lines.

#### 6.What is Demultiplexer?

A Demultiplexer is a circuit that receives information on a single line and transmits this information on one of  $2^n$  possible output lines

#### 7. Give the truth table for a half adder.

| Іпри |   | Output  |           |

|------|---|---------|-----------|

| X    | Y | Sum (S) | Carry (C) |

| 0    | 0 | 0       | 0         |

| 0    | 1 | 1       | 0         |

| L    | 0 | 1       | 0         |

|      | 1 | 0       | 1         |

#### Ove the truth table for a half Subtractor.

| Input |   | Output    |           |

|-------|---|-----------|-----------|

| X     | Y | Borrow(B) | Diffe (D) |

| 0     | 0 | 0         | 0         |

| 0     | 1 | 1         | 1         |

| 1     | 0 | 0         | 1         |

| 1     | 1 | 0         | 0         |

9. From the truth table of a half adder derive the logic equation

$$S = X \oplus Y$$

$$C = X \cdot Y$$

10. From the truth table of a half subractor derive the logic equation

$D = X \oplus Y$  $B = X^{1} \cdot Y$

11.From the truth table of a full adder derive the logic equation

$S = X \oplus Y \oplus Z$ C = XY + YZ + XZ

#### 12. What is code conversion?

If two systems working with different binary codes are to be synchronized in operation, then we need digital circuit which converts one system of codes to the other. The process of conversion is referred to as code conversion.

cor

#### 13. What is code converter?

It is a circuit that makes the two systems compatible even though each uses a different binary code. It is a device that converts binary signals from a source code to its output code. One example is a BCD to Xs3 converter.

#### 14. What do you mean by analyzing a combinational circuit?

The reverse process for implementing a Boolean expression is called as analyzing a combinational circuit. (ie) the available logic diagram is analyzed step by step and finding the Boolean function

#### 15. Give the applications of Demulaplexer.

- i) It finds its application in Data transmission system with error detection.

- ii) One simple application is binary to Decimal decoder.

#### 16.Mention the uses of Demultiplexer.

Demultiplexer is used in computers when a same message has to be sent to different receivers. Not only in computers, but any time information from one source can be fed to several places.

#### ve other name for Multiplexer and Demultiplexer.

Multiplexer is other wise called as Data selector.

Demultiplexer is otherwise called as Data distributor.

#### 18. What is the function of the enable input in a Multiplexer?

The function of the enable input in a MUX is to control the operation of the unit.

| 19.01ve the truth table for a full Subfractor. |                   |            |            |           |              |

|------------------------------------------------|-------------------|------------|------------|-----------|--------------|

|                                                | Input             |            | Out        | tput      |              |

| X                                              | Y                 | Z          | Borrow (B) | Diffe (D) |              |

| 0                                              | 0                 | 0          | 0          | 0         |              |

| 0                                              | 0                 | 1          | 1          | 1         |              |

| 0                                              | 1                 | 0          | 1          | 1         |              |

| 0                                              | 1                 | 1          | 1          | 0         |              |

| 1                                              | 0                 | 0          | 0          | 1         |              |

| 1                                              | 0                 | 1          | 0          | 0         | $\mathbf{C}$ |

| 1                                              | 1                 | 0          | 0          | 0         |              |

| 1                                              | 1                 | 1          | 1          | 1         |              |

| 20.Give the tr                                 | uth table for a f | ull adder. |            |           |              |

|                                                | Input             |            |            | tput      |              |

| Х                                              | Y                 | Z          | Sum (S)    | Carry (C) |              |

| 0                                              | 0                 | 0          | 0          | 0         |              |

| 0                                              | 0                 | 1          | 1          | 0         |              |

| 0                                              | 1                 | 0          |            | 0         |              |

| 0                                              | 1                 | 1          | 0          | 1         |              |

| 1                                              | 0                 | 0          | 1          | 0         |              |

| 1                                              | 0                 | 1          | 0          | 1         |              |

| 1                                              | 1                 | 0          | 0          | 1         |              |

| 1                                              | 1                 |            | 1          | 1         |              |

|                                                |                   |            |            |           |              |

#### 19. Give the truth table for a full Subtractor.

21.From the truth table of a full subtractor derive the logic equation

$$S = X \oplus Y \oplus Z$$

$$C = X^{1}Y + YZ + X^{1}Z$$

#### 22.What is priority encoder?

A priority encoder is an encoder that includes the priority function. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

#### 23. Can a decoder function as a Demultiplexer?

Yes. A decoder with enable can function as a Demultiplexer if the enable line E is taken as a data input line A and B are taken as selection lines.

#### 24.List out the applications of multiplexer?

The various applications of multiplexer are

- a. Data routing.

- b. Logic function generator.

- c. Control sequencer.

- d. Parallel-to-serial converter.

#### 25.List out the applications of decoder?

The applications of decoder are

- a. Decoders are used in counter system.

- b. They are used in analog to digital converter.

- c. Decoder outputs can be used to drive a display system.

#### 26.List out the applications of comparators?

The following are the applications of comparator

a. Comparators are used as a part of the address decoding circuitry in computers to select a specific input/output device for the storage of data.

b. They are used to actuate circuitry to drive the physical variable towards the reference value.

c. They are used in control applications.

#### 27. What are the applications of seven segment displays?

The seven segment displays are used in

- a. LED displays

- b. LCD displays

#### 28. What is digital comparator?

A comparator is a special combinational circuit designed primarily to compare the relative magnitude of two binary numbers.

2

#### 29. List the types of ROM.

- i) Programmable ROM (PROM)

- ii) Erasable ROM (EPROM)

- iii) Electrically Erasable ROM (EEROM)

#### 30.Differentiate ROM & PLD's

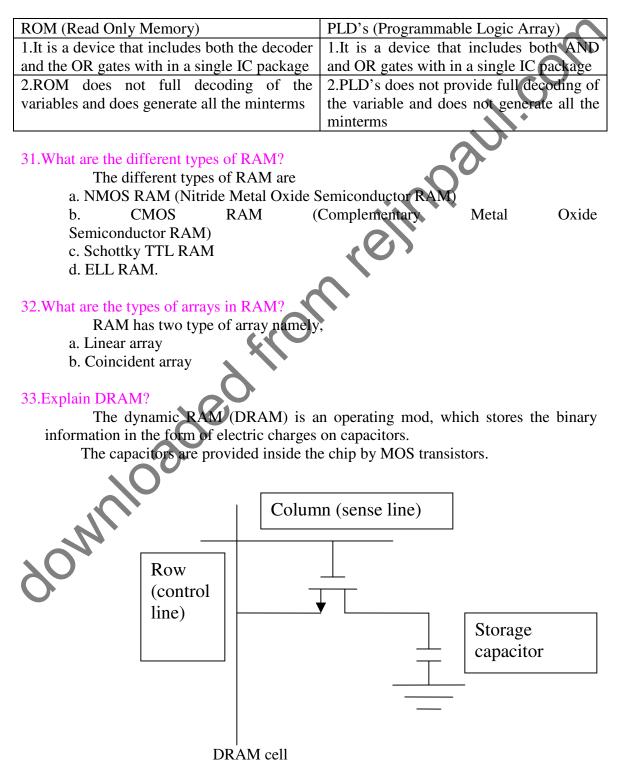

The stored charges on the capacitors tend to discharge with time and the capacitors must be tending to discharge with time and the capacitors must be periodically recharged by refreshing the dynamic memory.

DRAM offers reduced power consumption and larger storage capacity in a single memory chip.

#### 34.Explain SRAM?

Static RAM (SRAM) consists of internal latches that store the binary information. The stored information remains valid as long as the power is applied to the unit.

SRAM is easier to use and has shorter read and write cycle.

The memory capacity of a static RAM varies from 64 bit to 1 mega bit.

#### 35.Differentiate volatile and non-volatile memory?

| Volatile memory                         | Non-volatile memory                         |

|-----------------------------------------|---------------------------------------------|

| They are memory units which lose stored | It retains stored information when power is |

| information when power is turned off.   | turned off.                                 |

| E.g. SRAM and DRAM                      |                                             |

|                                         | E.g. Magnetic disc and ROM                  |

36.What are the terms that determine the size of a PAL?

The size of a PLA is specified by the

- a. Number of inputs

- b. Number of products terms

- c. Number of outputs

#### 37.What are the advantages of RAM?

The advantages of RAM are

- a. Non-destructive read out

- b. Fast operating speed

- c. Low power dissipation

- d. Compatibility

- e. Economy

#### N

#### What is VHDL?

VHDL is a hardware description language that can be used to model a digital system at many level of abstraction, ranging from the algorithmic level to the gate level.

The VHDL language as a combination of the following language.

- a. Sequential language

- b. Concurrent language

- c. Net-list language

- d. Timing specification

- e. Waveform generation language.

#### 39.What are the features of VHDL?

The features of VHDL are

- a. VHDL has powerful constructs.

- b. VHDL supports design library.

- c. The language is not case sensitive.

#### 40 What is meant by memory decoding?

The memory IC used in a digital system is selected or enabled only for the range of addresses assigned to it.

#### 41. What is access and cycle time?

eoperation of the terms of te The access time of the memory is the time to select word and read it. The cycle time of a memory is a time required to complete a write operation.

# **UNIT IV**

#### 1.What is sequential circuit?

Sequential circuit is a broad category of digital circuit whose logic states depend on a specified time sequence. A sequential circuit consists of a combinational circuit to which memory elements are connected to form a feedback path. Л. С

#### 2.List the classifications of sequential circuit.

- Synchronous sequential circuit. i)

- ii) Asynchronous sequential circuit.

#### 3.what is Synchronous sequential circuit?

A Synchronous sequential circuit is a system whose behavior can be defined from the knowledge of its signal at discrete instants of time. •

#### 4. What is clocked sequential circuits?

Synchronous sequential circuit that use clock pulses in the inputs of memory elements are called clocked sequential circuit. One advantage as that they don't cause instability problems.

#### 5.What is called latch?

Latch is a simple memory element, which consists of a pair of logic gates with their inputs and outputs inter connected in a feedback arrangement, which permits a single bit to be stored.

#### 6.List different types of

- SR flip-flop i)

- Clocked RS flip-flop ii)

- D flip-flop iii)

- T flip-flop iv)

- JK flip-flop

- JK master slave flip-flop

do you mean by triggering of flip-flop.

The state of a flip-flop is switched by a momentary change in the input signal. This momentary change is called a trigger and the transition it causes is said to trigger the flip-flop

#### 8.What is an excitation table?

During the design process we usually know the transition from present state to next state and wish to find the flip-flop input conditions that will cause the required transition. A table which lists the required inputs for a given chance of state is called an excitation table.

#### 9. Give the excitation table of a JK flip-flop

| Q(t) | Q(t+1) | J | K |

|------|--------|---|---|

| 0    | 0      | 0 | Х |

| 0    | 1      | 1 | Х |

| 1    | 0      | Х | 1 |

| 1    | 1      | Х | 0 |

#### 10. Give the excitation table of a SR flip-flop

|    | 1          | 0         | Х | 1   |                           |

|----|------------|-----------|---|-----|---------------------------|

|    | 1          | 1         | Х | 0   |                           |

| ab | le of a SR | flip-flop |   |     | COL                       |

| Γ  | Q(t)       | Q(t+1)    | S | R   |                           |

|    | 0          | 0         | 0 | Х   |                           |

|    | 0          | 1         | 1 | 0   | 20                        |

|    | 1          | 0         | 0 | 1   | $\mathbf{D}^{\mathbf{T}}$ |

|    | 1          | 1         | Х | • 0 | X                         |

| -  |            |           |   |     |                           |

11. Give the excitation table of a T flip-flop

| Q(t) | Q(t+1) | Т |

|------|--------|---|

| 0    | 0      | 0 |

| 0    |        | 1 |

| 1    | 0      | 1 |

| 1    | 1      | 0 |

|      |        |   |

12.Give the excitation table of a D hip-flop

| $\sim$   | Q(t) | Q(t+1) | Т |  |

|----------|------|--------|---|--|

|          | 0    | 0      | 0 |  |

| $\sim 0$ | 0    | 1      | 1 |  |

|          | 1    | 0      | 0 |  |

|          | 1    | 1      | 1 |  |

13. What is a characteristic table?

A characteristic table defines the logical property of the flip-flop and completely characteristic its operation.

14. Give the characteristic equation of a SR flip-flop.  $Q(t+1)=S+R^1Q$

15.Give the characteristic equation of a D flip-flop. Q(t+1)=D

16. Give the characteristic equation of a JK flip-flop.  $Q(t+1)=JQ^1+K^1Q$

17. Give the characteristic equation of a T flip-flop.  $Q(t+1)=TQ^{1}+T^{1}Q$

18. What is the difference between truth table and excitation table.

- i) An excitation table is a table that lists the required inputs for a given change of state.

- ii) A truth table is a table indicating the output of a logic circuit for various input states.

#### 19. What is counter?

A counter is used to count pulse and give the output in binary form.

#### 20.What is synchronous counter?

In a synchronous counter, the clock pulse is applied simultaneously to all flipflops. The output of the flip-flops change state at the same instant. The speed of operation is high compared to an asynchronous counter

#### 21. What is Asynchronous counter?

In a Asynchronous counter, the clock pulse is applied to the first flip-flops. The change of state in the output of this flip-flop serves as a clock pulse to the next flip-flop and so on. Here all the flip-flops do not change state at the same instant and hence speed is less.

#### 22 What is the difference between synchronous and asynchronous counter?

| Sl.No. | Synchronous counter                   | Asynchronous counter                                                                                          |

|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1.     | Clock pulse is applied simultaneously | Clock pulse is applied to the first<br>flip-flop, the change of output is<br>given as clock to next flip-flop |

| 2.     | Speed of operation is high            | Speed of operation is low.                                                                                    |

#### 23.Name the different types of counter.

Synchronous counter

Asynchronous counter

- i) Up counter

- ii) Down counter

- iii) Modulo N counter

- iv) Up/Down counter

#### 24 What is up counter?

A counter that increments the output by one binary number each time a clock pulse is applied.

#### 25.What is down counter?

A counter that decrements the output by one binary number each time a clock pulse is applied.

#### 26.What is up/down counter?

A counter, which is capable of operating as an up counter or down counter, depending on a control lead.

#### 27.What is a ripple counter?

A ripple counter is nothing but an asynchronous counter, in which the output of the flip-flop change state like a ripple in water.

#### 28. What are the uses of a counter?

- i) The digital clock

- ii) Auto parking control

- iii) Parallel to serial data conversion.

#### 29. What is meant by modulus of a counter?

By the term modulus of a counter we say it is the number of states through which a counter can progress.

#### 30.what is meant by natural count of a counter?

By the term natural count of a counter we say that the maximum number of states through which a counter can progress.

#### 31.A ripple counter is a ----- sequential counter.

Ans: Synchronous.

#### 32. What is a modulo counter?

A counter that counts from 0 to T is called as modulo counter.

33.A counter that counts from the T is called a modulo counter. True or False. Ans: True

34. The number of Thio Hops required for modulo-18 counter is ------Ans: five.

35.Form the truth table for 3-bit binary down counter.

| Clk | Q2 | Q1 | Q0 |

|-----|----|----|----|

| 1   | 1  | 1  | 1  |

| 1   | 1  | 1  | 0  |

| 1   | 1  | 0  | 1  |

| 1   | 1  | 0  | 0  |

| 1   | 0  | 1  | 1  |

| 1   | 0  | 1  | 0  |

| 1   | 0  | 0  | 1  |

| 1   | 0  | 0  | 0  |

| 1   | 1  | 1  | 1  |

#### 36. What is a ring counter?

A counter formed by circulating a 'bit' in a shift register whose serial output has been connected to its serial input.

#### 37.What is BCD counter?

A BCD counter counts in binary coded decimal from 0000 to 1001 and back to 0000. Because of the return to 0000 after a count of 1001, a BCD counter does not have a regular pattern as in a straight binary counter.

#### 38. What are the uses of a ring counter?

- i) Control section of a digital system.

- ii) Controlling events, which occur in strict time sequence.

#### 39.What is a register?

Memory elements capable of storing one binary word. It consists of a group of flip-flops, which store the binary information.

#### 40.What is Johnson counter?

It is a ring counter in which the inverted output is fed into the input. It is also know as a twisted ring counter.

#### 41. What is a shift register?

In digital circuits, datas are needed to be moved into a register (shift in) or moved out of a register (shift out). A group of flip-flops having either or both of these facilities is called a shift register.

#### 42. What is serial shifting?

In a shift register, if the data is moved 1 bit at a time in a serial fashion, then the technique is called serial shifting.

#### 43. What is parallel shifting?

In a shift register all the data are moved simultaneously and then the technique is called parallel shifting.

#### 44. Write the uses of a shift register.

Temporary data storage Bit manipulations.

#### 45. What is a cycle counter?

A cycle counter is a counter that outputs a stated number of counts and then stops.

#### 46. Define state of sequential circuit?

The binary information stored in the memory elements at any given time defines the "state" of sequential circuits.

#### 47. Define state diagram.

A graphical representation of a state table is called a state diagram.

#### 48. What is the use of state diagram?

- i) Behavior of a state machine can be analyzed rapidly.

- ii) It can be used to design a machine from a set of specification.

#### 49. What is state table?

A table, which consists time sequence of inputs, outputs and flip-flop states, is called state table. Generally it consists of three section present state, next state and output.

#### 50. What is a state equation?

A state equation also called, as an application equation is an algebraic expression that specifies the condition for a flip-flop state transition. The left side of the equation denotes the next state of the flip-flop and the right side; a Boolean function specifies the present state.

#### 51. What is meant by race around condition?

In JK flip-flop output is fed back to the input, and therefore changes in the output results change in the input. Due to this in the positive half of the clock pulse if J and K are both high then output toggles continuously. This condition is known as race around condition.

around condition.

# UNIT V

#### 1. What is flow table?

During the design of synchronous sequential circuits, it is more convenient to name the states by letter symbols without making specific reference to their binary values. Such table is called Flow table.

#### 2. What is primitive flow table?

A flow table is called Primitive flow table because it has only one stable state in each row.

#### 3. Define race condition.

A race condition is said to exist in a synchronous sequential circuit when two or more binary state variables change, the race is called non-critical race.

#### 4. Define critical & non-critical race with example.

The final stable state that the circuit reaches does not depend on the order in which the state variables change, the race is called non-critical race.

The final stable state that the circuit reaches depends on the order in which the state variables change, the race is called critical race.

#### 5. How can a race be avoided?

Races can be avoided by directing the circuit through intermediate unstable states with a unique state – variable change.

#### 6. Define cycle and mergins?

When a circuit goes through a unique sequence of unstable states, *i*t is said to have a cycle.

The grouping of stable states from separate rows into one common row is called merging.

#### 7. Give state – reduction procedure.

The state – reduction procedure for completely specified state tables is based on the algorithm that two states in a state table can be combined in to one if they can be shown to be equivalent.

#### 8. Define hazards.

Hazards are unwanted switching transients that may appear at the output of a circuit because different paths exhibit different propagation delays.

#### 9. Does Hazard occur in sequential circuit? If so what is the problem caused?

Yes, Hazards occur in sequential circuit that is Asynchronous sequential circuit. It may result in a transition to a wrong state. 10. Give the procedural steps for determining the compatibles used for the purpose of merging a flow table.

The purpose that must be applied in order to find a suitable group of compatibles for the purpose of merging a flow table can be divided into 3 procedural steps.

- Determine all compatible pairs by using the implication table. i.

- ii. Find the maximal compatibles using a Merger diagram

- iii. Find a minimal collection of compatibles that covers all the states and is aul. closed.

#### 11. What are the types of hazards?

The 3 types of hazards are 1) Static -0 hazards

2) Static – 1 hazard

3) Dynamic hazards

#### 12. What is mealy and Moore circuit?

Mealy circuit is a network where the output is a function of both present state and input.

Moore circuit is a network where the output is function of only present state.

#### 13.Differentiate Moore circuit and Mealy circu

| Moore circuit                                  | Mealy circuit                                  |

|------------------------------------------------|------------------------------------------------|

| a. It is output is a function of present state | a. It is output is a function of present state |

| only.                                          | as well as the present input.                  |

| X                                              | b. Input changes may affect the output of      |

| b. Input changes do not affect the output.     | the circuit.                                   |

| c. Moore circuit requires more number of       | c. It requires less numbers of states for      |

| states for implementing same function.         | implementing same                              |

|                                                | function.                                      |

#### 13. How can the hazards in combinational circuit be removed?

Hazards in the combinational circuits can be removed by covering any two min terms that may produce a hazard with a product term common to both. The removal of hazards requires the addition of redundant gates to the circuit.

#### does an essential hazard occur?

An essential hazard occurs due to unequal delays along two or more paths that originate from the same input. An excessive delay through an inverter circuit in comparison to the delay associated with the feedback path causes essential hazard.

#### 15.what is Timing diagram?

Timing diagrams are frequently used in the analysis of sequential network. These diagrams show various signals in the network as a function of time.

#### 16. What is setup and hold time?

The definite time in which the input must be maintained at a constant value prior to the application of the pulse is setup time

The definite time is which the input must not chance after the application of the positive or negative going transition of the pulse based on the triggering of the pulse.

#### 17.Define bit time and word time.

The time interval between clock pulses is called bit time.

The time required to shift the entire contents of a shift register is called word time.

#### 18.What is bi-directional shift register and unidirectional shift register?

A register capable of shifting both right and left is called bi-directional shift register.

A register capable of shifting only one direction is called unidirectional shift register.

#### 19.Define equivalent state.

If a state machine is started from either of two states and identical output sequences are generated from every possible set of sequences, then the two states are said to be equivalent.

#### 20.a shift register can be operated in all possible ways then it is called as------

Ans: Universal register: It can be operated in all possible modes with bidirectional shift facility.

#### 21 What is gate delay?

If the change in output is delayed by a time  $\varepsilon$  with respect to the input. We say that the gate has a propagation delay of  $\varepsilon$ . Normally propagation delay for 0 to 1 output ( $\varepsilon$ 1) may be different than the delay for 1 to 0 changes ( $\varepsilon$ 2).

#### 22.Define state reduction algorithm.

State reduction algorithm is stated as "Two states are said to be equivalent if, for each member of the set of inputs they give the same output and send the circuit either to the same state or to an equivalent state. When two states are equivalent, one of them can be removed without altering the input-output relation.

#### 23. What is meant by level triggering?

In level triggering the output of the flip-flop changes state or responds only when the clock pulse is present.

#### 24.Write the uses of a shift register.

i) Temporary data storage.

ii) Bit manipulations.

#### 25. What is meant by flow table?

During the design of asynchronous sequential circuits, it is more convenient to name the states by letter symbols without making specific reference to their binary values. Such a table is called a flow table.

#### 26. What are the problems involved in asynchronous circuits?

The asynchronous sequential circuits have three problems namely,

- a. Cycles

- b. Races

- c. Hazards

#### 27. Define cycles?

If an input change includes a feedback transition through more than unstable state then such a situation is called a cycle.

#### 28. Define primitive flow table?

A primitive flow table is a flow table with only one stable total state in each row. Remember that a total state consists of the internal state combined with the input.

#### 29. Define merging?

The primitive flow table has only one stable state in each row. The table can be reduced to a smaller numbers of rows if two or more stable states are placed in the same row of the flow table. The grouping of stable states from separate rows into one common row is called merging.

mer.

# PART B

### UNIT I

- 1 (i). Express the Boolean function F = A+B'C in sum of minterms

- (ii) Express the Boolean function F =A+B'C in sum of minterms

(ii) Express the Boolean function F=xy+x'z in production of maxterms.

Solution: F = A+B'C = A'B'C'+AB'C' AB'C ,ns. QQUI

- $= m_1 + m_4 + m_5 + m_6 + m_7$  $=\Sigma m (1,4,5,6,7)$

- F = XY + X'Z= (X+Y+Z)(X+Y'+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Y+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z)(X'+Z $= M_0 M_2 M_4 M_5$  $= \Pi (0,2,4,5)$

- 2.Simplify the Boolean function  $F(A,B,C,D) = \sum (0,6,8,13,14)$  Together with the don't care condition  $d=\sum(2,4,10)$  and then express the simplified function in sum of minterms.

Using 4-variable map simplify the function as F=B'D'+CD'+ABC'D Represent the simplified function in SOP from as  $F=\Sigma(0,2,6,8,10,13,14)$

3.Implement the Boolean function F(X,Y,Z)=(1,2,3,4,5,7) with NAND gates

Simplify the function using 3-varabile map and express it SOP from as F=XY'+X'Y+Z

Draw a NAND gate for each product term of the expression. This gives a group of first level gates.

• Draw a single gate using the AND –invert or the invert -OR graphic simple in the second level, with inputs coming from outputs of first level gates.

- 4. Simplify the Boolean function  $F(A,B,C,D) = \sum (0,2,3,5,7,8,9,10,11,13,15)$  and find the prime implicants and essential prime implicants

- Simplify the expression using 4-varible map,

- Prime implicants are :CD,B'C,AD AND AB'

- Essential prime implicants are :CD,B'C,AD AND AB'

- Different simplified versions are :BD and B'D'

F=BD+B'D+CD+AD F=BD+B'D+CD+AB' F=BD+B'D+B;C+AD F=BD+B'D'+B;C+AB'

5. Minimize the following function sing Quine Mc Cluskey Method

- List all minterms in the binary form

- Arrange minterms according to categories of 1 in a table

- Compare each binary number with every term in the next higher category and if they differ only one position put a check mark and copy the term in the next column with a in the position that they differed.

- Continue the process until no further elimination of literals

- List the prime implicants

- Select the minimum number of prime implicants

### UNIT

1.Design a full adder with inputs x,y,z and two outputs S and C. The circuit performs x+y+z, z is the input carry, C is the output carry and S is the Sum.

- Truth table for full adder

- Simplify using K map

- Draw the logic diagram using AND and XOR gate

- Draw the logic diagram using 2 half adders

- 2. Design a BCD adder.

- Explanation on BCD addition

- Add 2 BCD numbers using ordinary binary addition

- $\circ$  If sum >=9 no correction is needed

- $\circ$  If sum >=9 or if a carry is generated the sum is invalid

- $\circ$  To correct the invalid sum add 0110 to the sum. If a carry results from this addition add it to the next higher order BCD digits.

- Draw the truth table with 4 inputs

- Simplify output using 4 variable map

- Draw the logic diagram

```

http://auengineeringnotes.wix.com/ausub-studymaterial

```

- 3. Design a logic circuit that accepts a 4-bit Grey code and converts it into 4-bit binary code

- Draw the truth table with 4 inputs G3,G2,G1andG0 and 4 0utputs D,C,B and A.

- Simplify the columns A,B,C and D using 4-variables map A=(G3 XOR G2)XOR(G1 XOR G0) B=G3 XOR G2 XOR G1 C=G3 XOR G2 D=G3

- Draw the logic diagram using xor gates with G3,G2,G1 and G0 as Input and A,B,C and D as output

4. Write short notes on: BCD adder, Binary multiplier and Magnitude Comparator

- BCD adder truth table

- Block diagram of BCD adder

- Logic diagram for 2-bit by 2-bit binary multiplier

- 4-bit magnitude comparator

- 5.Explain in detail the Hardware Description Languages

- Module representation

- Gate delays

- Boolean expressions

- User -defined primitives

- Explanation of the above with suitable examples

### **UNIT-III**

1.Draw the circuit for 3-to-8-decoder and implement the functions

F1(A,B,C)=II(0,1,3,7) F2(A,B,C)=II(2,3,7) using 3-to-8-decoder

- Truth table for a 3-to-8-decoder(i/p: E,A,B,C and o/p:Y7-Y0)

- Logic diagram

- Block diagram of 3:8 decoder using IC74LS183 WITH A,B,C as input and F1,F2 as output

- 2.Draw the circuits for Decimal to BCD encoder, Octal-to-Binary encoder & Priority encoder

- Decimal to BCD encoder-logic symbol(74LS147,truth table)

- Octal to binary encoder truth table with inputs D0 D7 and outputs A , B and C

- Logic diagram of Octal to binary encoder: A=D4+D5+D6+D7; B=D2+D3+D6+D7; C=D1+D3+D5+D7

- Priority encoder truth table with i/ps : D0,D1,D2,D3 and o/ps: Y1,Y0

- Logic diagram of Priority encoder where Y1=D2+D3,Y0=D3+D1D2

V=D1+D2+D3

3.Implement the following boolean function using 8:1 multiplier

- F(A,B,C,D)=A'BD'+ACD+B'CD+A'B'CD+A'BC'D+A'B'C'D

- Draw the Truth table for the above SOP(I/P's:A,B,C,D, o/p: Y)

- Draw the implementation table 8:1 multiplexer, where D0=0,D2=0,D1=D3=1,D4=D5=D6=A',D7=A

4.Implement full subtractor using demultiplexer

- Truth table of full subtractor(i/p;A,B,Bin,o/pL:D,Bout)

- D=F(A,B,C)=m(1,2,4,7)

- Bout=F(A,B,C)= m(1,2,3,7)

- Draw 1:8 demultiplexer with the input Din=1 and output D and Bout.

5.Implement the following Boolean function with a PLA F1(A,B,C) = m(0,1,2,4) F2(A,B,C) = m(0,5,6,7)

Simplify F1 and F2 using k-map F1(A,B,C)=(AB+AC+BC)' F2(A,B,C)=AB+AC+A'B'C'

Draw the PLA programming table with minterms AB,AC,BC&A'B'C'

### UNIT IV

1. Draw the state diagram and characteristic equations of T,D and JK flip flop

- Characteristic equation of T flip flop: Q(t+1)=TQ'+T'Q

- Characteristic equation of D flip flop: Q(t+1)=D

- Characteristic equation of JK flip flop: Q(t+1)=JQ'+K'Q

- state diagrams of T,D and JK flip flops

2. Write short notes on state reduction and state assignment in Sequential circuit design

State reduction

- Given a state diagram of a sequential circuit. Establish the corresponding state table

- Find the equivalent states that produce the same output for even input and the same next state

- Draw the reduced state table by removing one of the equivalent state

- Draw the corresponding reduced state diagram

State assignment

- Binary assignment

- Gray code assignment

- One-hot assignment

3. Discuss in detail shift registers

- Block diagram of 4-bit shift register

- Serial transfer of information

- serial addition using shift register

- Universal shift register

- 4.Discuss about synchronous counters

- binary counter:4-bit synchronous binary counter, with parallel load

Up-down counter

- BCD counter

5.Write the procedure for analyzing a clocked sequential circuit with JK flip flop

- Given a logic diagram. From this ,write the state equations

- Establish the state table

- Draw the state diagram

- Write the flip flop input equations and the output equation, if any.

### UNIT -V

- 1.Explain the procedure for analyzing an asynchronous sequential circuit with SR latches with example

- Given an asynchronous sequential circuit with SR latch

- Label each latch output with Yi and its external feedback path with Yi

- Derive the Boolean functions for the Si & Ri input in each latch

- check whether SR=0 for each NOR latch or whether S'R' =0 for each NAND latch

- Evaluate Y=S+R'y for each NOR latch or Y=S'+Ry for each NAND latch

- Construct a map with the y's representing the rows and the x inputs representing the columns

- Plot the value of Y=Y1Y2.....in the map

- Circle all stable states where Y=y. The resulting map is then the transition table.

- 2.Explain the procedure for designing an asynchronous sequential circuit with an example obtain a primitive flowtable from the given design specifications

- Reduce the flow table by merging rows in the primitive flowtable

- Assign binary values to the state variables to obtain the transition tables Assign output values to unstable states to obtain the output maps

- Simplify the Boolean functions of the excitations and output variables and draw the logic diagram.

3.Discuss in detail the procedure for reducing the flowtable with an example

- Determine all the compatible pairs by using implication table

- Find the maximal compatibles using the merger diagram

- Find the minimal collection of compatibles that covers all the states and is closed

- The minimal collection is used to merge the rows of the flow table

4.write short notes on race-free state assignment

- Three row flowtable example

- Four row flowtable example

- shared row method

- Multiple row method

5.Explain in detail Hazards

- Hazards in combinational circuits

- Explanation with example

- (Static 1-Hazard, Static 0-Hazard&Dynamic Hazard)

- Hazards in sequential circuit

- Implementation with SR latches